在短短几年内,大语言模型的规模膨胀了超过400倍,而同期硬件内存的扩展仅实现了2倍增长,这一巨大差距为存储行业带来了前所未有的挑战。QXtesmc

为应对这一挑战,新型内存技术如HBM4、GDDR7和DDR5等正在推出,它们提供了更高的带宽和更大的容量,以适应市场的快速扩张,尤其是在人工智能领域。在追求性能和容量提升的同时,提高能效也是一项关键的技术难题,呼唤着持续的创新。QXtesmc

最近,Rambus推出了业界首个HBM4控制器IP,这一里程碑式的产品进一步巩固了公司在内存接口技术的前沿地位。该控制器IP针对新一代HBM内存量身定制,显著提升了数据传输速率和内存容量,为AI加速器、图形处理器以及高性能计算应用提供了坚实的性能基础。QXtesmc

AI训练和AI推理对内存的新要求

Rambus研究员兼杰出发明家Steven Woo博士展示了一些实例,说明客户如何在数据中心使用Rambus的产品。他介绍说,AI训练和AI推理对内存的新要求。AI包含两个主要步骤:训练和推理。这两个阶段对内存性能的需求各有侧重,推动了内存技术的持续进步。QXtesmc

在训练阶段,AI通过分析大量数据来学习规律并构建模型,例如,通过分析猫、鸟、马的图片来学会识别这些动物。由于AI训练需大量数据,整个过程相当漫长,常需数周至数月。在面对复杂模型时,如实时语言处理和生成式语言模型,由于其规模较大,训练周期会更长。QXtesmc

AI训练是计算领域极具挑战的任务,在这个阶段涉及海量数据处理。而快速完成训练,能让模型尽早投入使用,加速投资回报并提升回报率。这对内存提出了更高的要求,必须确保其具备快速的响应速度、卓越的性能表现,同时体积还需小巧紧凑。QXtesmc

在训练完成后,模型可应用于实际场景,处理新案例进行推理,即AI的推理阶段。此阶段对速度和准确性有高要求,期望模型能迅速准确提供结果。AI推理阶段对内存的要求尤为严苛,需实现更低的延迟和更高的带宽,以确保推理结果能够实时快速输出。QXtesmc

数据显示,自2012年以来,内存对速度、容量和尺寸的要求每年以超过10倍的速度提升,这一趋势未见放缓。以大型语言模型GPT为例,其参数量和规模在过去几年里显著增长。QXtesmc

以GPT模型为例,2022年11月发布的GPT-3含有1,750亿参数,而到了2024年5月,GPT-4o的参数量已超过1.5万亿。短短几年间,大语言模型的规模扩大了400倍以上。然而,同期硬件内存的规模仅增长了2倍,这对存储行业带来了极大的挑战。为了满足这些AI模型对内存容量和带宽的巨大需求,业界不得不增加GPU和AI加速器的数量。QXtesmc

先进内存系统是如何应用于AI的?

QXtesmc

QXtesmc

当前,最先进的内存系统在AI系统中的应用及其相互间的差异与共同点值得关注。QXtesmc

- DDR内存,作为目前最普遍的内存类型,已被广泛部署于全球的服务器和数据中心中。

- LPDDR,即低功耗DDR内存,最初是为移动设备量身定制的。然而,大家逐渐发现,LPDDR不仅适用于手机,也在AI边缘推理系统中有出色表现。

- GDDR,专为图形处理设计的DDR内存,现在也被广泛应用于AI推理任务。它在带宽、成本和可靠性之间取得了良好的平衡,因此已被用于汽车和一些网络应用领域。

- HBM拥有远超传统DRAM的极高带宽和密度。这种内存特别适合于AI训练、高性能计算和网络应用。

不同的内存类型各有其特定的应用场景,AI系统通常会根据具体的应用需求选择合适的内存类型。QXtesmc

QXtesmc

QXtesmc

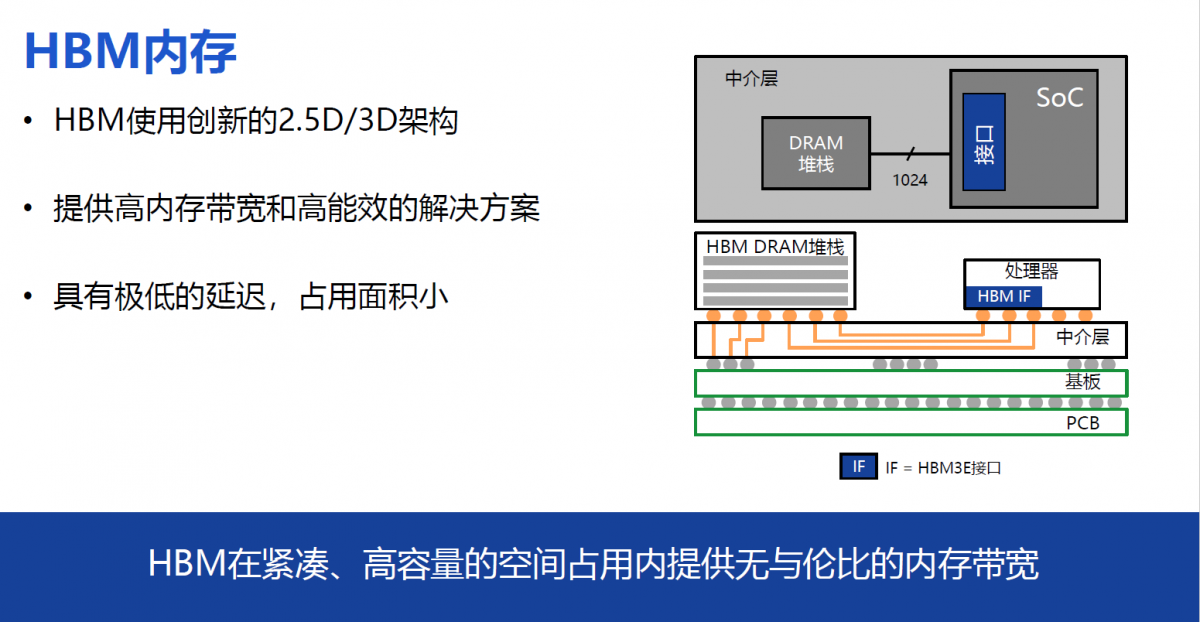

上图可以看到HBM内存的构造,以及它如何与芯片处理器和SoC连接——HBM的DRAM内存通过一个中间层物理连线与处理器连接。右边展示的橙色线条所贯穿的中介层,这部分共同连接到一个基板,然后基板焊接在PCB上。HBM的DRAM堆栈采用多层堆叠架构,这种方式能够提供极高的内存带宽、容量和能效。在这里,会有大量的芯片堆叠,其中一个内存芯片直接与处理器相连。在HBM3标准中,HBM内存的一个显著特点是它拥有大量连接到SoC的线,在HBM3中达到了1024根线。QXtesmc

随着命令、地址、时钟和其他附加信号的增加,HBM3所需的信号路径数量上升至大约1700条。这一数量远远超出了标准PCB的承载能力。因此,采用硅中介层作为桥梁,将内存设备与处理器连接。类似于集成电路,硅中介层能够蚀刻出极小间距的信号路径,从而实现所需的信号线数量,以满足HBM接口的要求。正是这种精细的结构设计以及HBM DRAM的堆叠技术,使得HBM内存能够提供极高的内存带宽、出色的能效、极低的延迟,并且在占用空间上达到最小化。QXtesmc

QXtesmc

QXtesmc

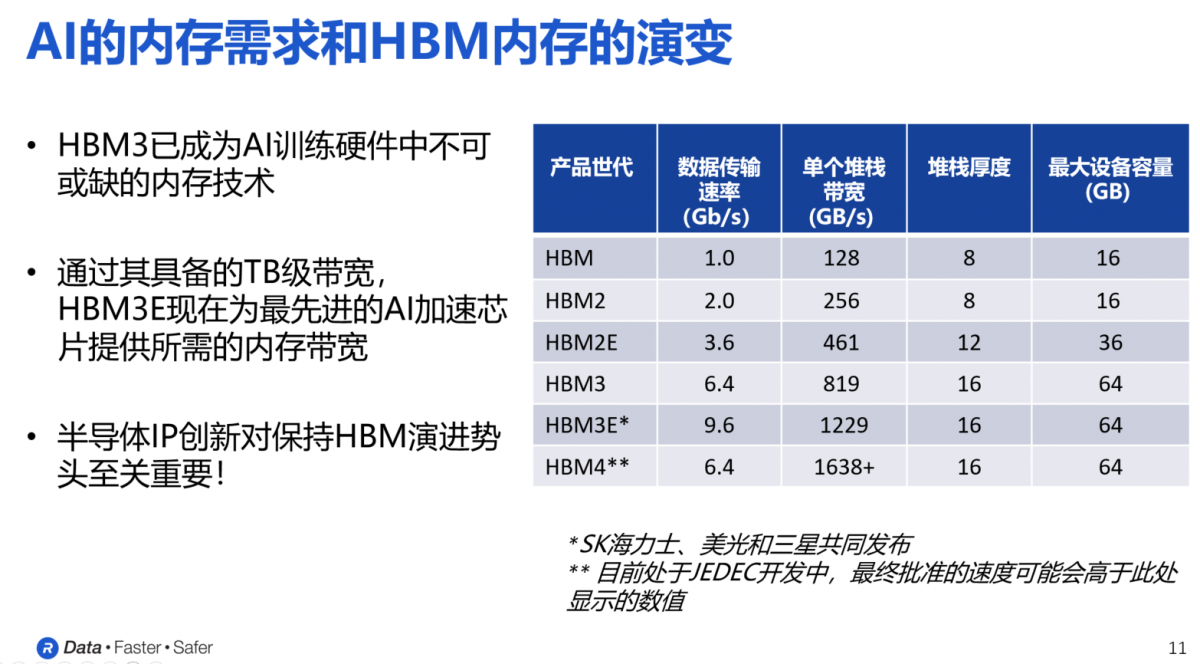

上图展示了HBM内存的发展历程,以及HBM4如何继承前代的优秀特性并实现进一步的提升。右侧的表格中是不同代HBM内存的数据传输速度、单个堆栈的带宽、堆栈厚度以及最大设备容量等具体参数。QXtesmc

从HBM的第一代发展到第二代、2E、3E,每一代的显著进步体现在单个堆栈带宽的显著提升。HBM3E的单个设备带宽已超过1.2TB/s。HBM3设备正日益普及,主要DRAM制造商,包括SK海力士、美光和三星,均已宣布推出HBM3E设备,其数据传输速率高达9.6Gbps。在追求高带宽内存的驱动下,内存行业持续进步,致力于开发新一代HBM内存。QXtesmc

目前,正处于开发阶段的HBM4,是由JEDEC制定标准的下一代技术。虽然HBM4的各项参数尚在开发阶段,但每个堆栈的带宽已经超越HBM3E。从单个堆栈的角度分析,HBM4的带宽预计将达到1.6TB/s,这仅是单个堆栈的带宽,实际的总带宽有可能更高。随着行业不断推出更快速的HBM内存器件,Rambus作为内存控制器IP提供商将在这一进程中扮演关键角色。QXtesmc

随着AI的发展,未来内存技术将遭遇哪些新挑战或机遇?Steven Woo提到,未来内存技术将面临提供更多带宽和容量的挑战。新型内存,如HBM4、GDDR7、DDR5等,正在提供更高的带宽和更大的容量,以满足市场的持续增长需求,特别是在人工智能领域。除了提升性能和容量,提高能效也是一个具有挑战性的领域,需要不断的技术创新。QXtesmc

在Rambus,产品部门和研究机构Rambus Labs都在努力满足市场对人工智能的内存需求。据了解,Rambus Labs专注于未来的内存需求,其研究议程包括探索如何提升未来人工智能内存的速度、容量和能效。通过这些部门的共同努力,Rambus期望能够满足人工智能领域的近期和未来几年的需求。QXtesmc

发布业内首款HBM4控制器IP,为客户一次流片成功保驾护航

日前,Rambus宣布推出业内首个HBM4控制器IP。Steven Woo表示,基于该IP的HBM4控制器能够支持新一代HBM内存的实施,适用于尖端的处理器,包括AI加速器、图形处理器,以及高性能计算应用。QXtesmc

HBM4内存解决方案在HBM3性能的基础上实现了进一步的提升。具体来看,HBM4的控制器IP提供了一个拥有32个独立通道的接口,总数据宽度可达2048位。基于这一数据宽度,当数据速率为6.4Gbps时,HBM4的总内存吞吐量将比HBM3高出两倍以上,达到1.64TB/s。与HBM3E控制器相似,HBM4内存控制器IP也是一个模块化、高度可配置的解决方案。QXtesmc

QXtesmc

QXtesmc

针对客户特定应用场景的独特需求,Rambus还提供定制化服务,覆盖尺寸、性能和功能等多个方面。关键的可选功能包括ECC(错误校正码)、RMW(读-改-写)和错误清理等。QXtesmc

此外,为了确保客户能够根据需求选择并集成各种第三方PHY到系统中,Rambus还与顶尖的PHY供应商建立了合作关系,保障客户在开发过程中能够实现一次性流片成功。总之,Rambus推出的HBM4控制器IP是基于多年来在HBM内存领域的深厚积累。QXtesmc

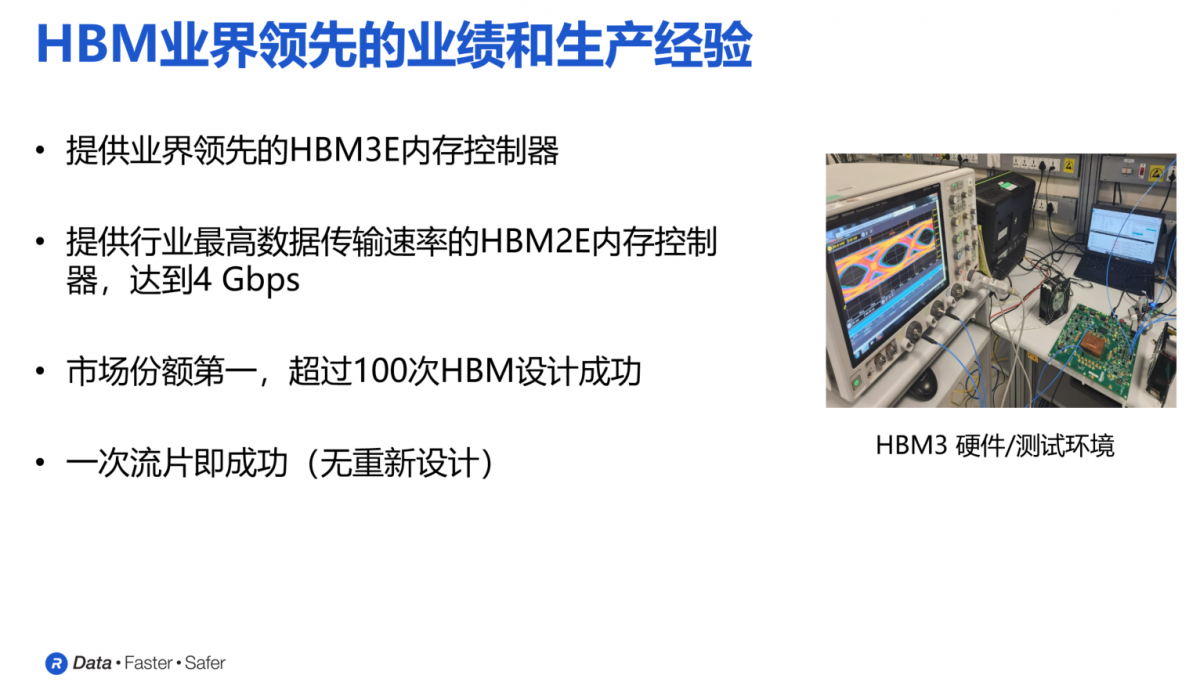

Rambus是如何做到实现一次流片成功的?据介绍,高公司通过控制器测试平台、验证IP、物理层(PHY)支持三方面来支撑。QXtesmc

QXtesmc

QXtesmc

比如,控制器测试平台使得用户能够执行完整的控制器代码库回归测试。该公司提供了广泛的测试序列,这些序列能够针对特定控制器和PHY进行测试,并且实施了基于功能覆盖率的验证计划来保障测试的完整性。QXtesmc

又如,Rambus还提供了验证IP,并与Avery Design Systems(现为西门子的一部分)合作,供应包括内存模块、主机内存控制器和PHY BFM在内的多种BFM。鉴于物理层PHY支持的重要性,该公司为多种第三方PHY提供了广泛的支持,确保其控制器与不同PHY之间的匹配、认证和验证,从而便利客户的集成工作。QXtesmc

Rambus的半导体IP解决方案组合

除了以上信息之外,Rambus还展示了其半导体IP解决方案组合,这些方案广泛应用于AI、高性能计算和先进处理领域。QXtesmc

根据Rambus大中华区总经理苏雷的介绍,Rambus在半导体产业链中扮演着关键角色,提供接口与安全IP技术,拥有2800项专利,专注于DDR4和DDR5内存模块的解决方案。过去五年,公司产品收入的复合年增长率达到42%,并荣获GSA年度尊重奖项。QXtesmc

QXtesmc

QXtesmc

该公司所提供的内存接口解决方案,包括GDDR和HBM内存控制器等,其芯片到芯片控制器IP产品组合涵盖PCIe和CXL等技术。与此同时,Rambus还提供广泛的安全IP产品,保护硬件和数据安全,包括Root of Trust(RoT)和MACsec IP。QXtesmc

据介绍,Rambus的认证解决方案适用于汽车、IoT和政府等行业,其IP解决方案在功耗和面积上经过优化,并由专业团队支持,确保客户首次流片成功。此外,Rambus还为了补充其内存控制器产品线,推出了内存内加密(IMI)解决方案,确保数据在加速器和内存之间传输的安全性。通过PCIe或CXL连接处理器时,Rambus还提供数据完整性和加密功能,保障数据链路传输的安全。QXtesmc

综合这些技术,Rambus的IP产品组合提供了高带宽解决方案,实现数据从内存到处理器的快速传输,并确保处理器与设备之间数据传输的高速性。同时,Rambus通过提供保护数据在静态、使用和传输过程中的IP,确保了数据的安全性。QXtesmc

小结:

综上所述,随着大语言模型规模的迅速扩张,内存技术面临的挑战日益严峻。新型内存技术如HBM4、GDDR7和DDR5的发展,为AI和高性能计算领域提供了更高的带宽和更大的容量,满足了市场的快速需求。Rambus等公司在内存接口和安全IP技术方面的创新,不仅推动了整个行业的技术进步,也为数据处理速度和安全性提供了保障。展望未来,内存技术的持续发展将是支持AI和高性能计算应用的关键,同时也需要整个行业共同面对能效提升和安全性增强的挑战。QXtesmc

责编:Clover.li