一文读懂台积电上海技术论坛

继美洲、欧洲、中国台湾等地的年度技术论坛之后,台积电日前再度回到上海召开年度技术论坛,分享了其最新的技术路线以及对产业未来趋势的看法,台积电总裁魏哲家、台积电中国总经理罗镇球等高层悉数到场。

2022年,台积公司与其合作伙伴共创造了超过12,000种创新产品,运用近300种不同的台积公司技术。持续投资先进逻辑工艺、3DFabric和特殊制程等技术,在适当的时间提供合适的技术,协助推动客户创新,是台积电向业界做出的承诺。oyqesmc

但本次活动并未邀请媒体参加,台积电方面给出的原因是“技术论坛只面向用户开放”。会后,《国际电子商情》拿到了一份媒体背景资料,经整理后与广大读者分享。oyqesmc

深耕先进工艺

台积电方面认为,随着 AI、5G和其他先进工艺技术的发展,全球正通过智能边缘网络产生大量的运算工作负载,需要更快、更节能的芯片来满足此需求。预计到2030年,因需求激增,全球半导体市场将达到约1万亿美元规模,其中高性能计算(HPC)相关应用占40%、智能手机占30%、汽车占15%、物联网占10%。oyqesmc

随着台积电的先进工艺技术从10纳米发展至2纳米,其能源效率在十年间以15%的年复合增长率提升,以支持半导体产业的惊人成长。同时,台积电先进工艺技术的产能年复合增长率在2019年至2023年间将超过40%。oyqesmc

作为第一家于2020年开始量产5纳米的晶圆厂,台积电通过推出N4、N4P、N4X 和 N5A等技术,持续强化其5纳米工艺家族。而在移动和HPC应用驱动下,其3纳米工艺作为半导体产业中第一个实现高量产和高良率的工艺技术,也将快速、顺利地实现产能提升(ramping)。2024年和2025年,台积公司还将推出N3P和N3X来提升工艺技术价值,在提供额外性能和面积优势的同时,保持了与N3E的设计规则兼容性,能够最大程度地实现IP复用。oyqesmc

先进制程的缺陷密度(D0)和每百万件产品缺陷数(DPPM)是衡量晶圆厂制造卓越性的两大重要指标。数据显示,尽管N5工艺复杂度远高于N7,但在相同阶段,N5的良率优化比N7更好;N3工艺技术的D0效能已经与N5同期的表现相当;N7和N5制程技术在包括智能手机、电脑和汽车等方面展现了领先业界的DPPM,N3的DPPM将很快就能追上N5的表现。oyqesmc

此外,台积电还推出了业界第一个基于3纳米的Auto Early技术,命名为N3AE,并提供以N3E为基础的汽车制程设计套件(PDK),让客户能够提早采用3纳米技术来设计汽车应用产品,以便于2025年及时采用届时已全面通过汽车制程验证的N3A工艺技术。oyqesmc

TSMC 3DFabricTM技术

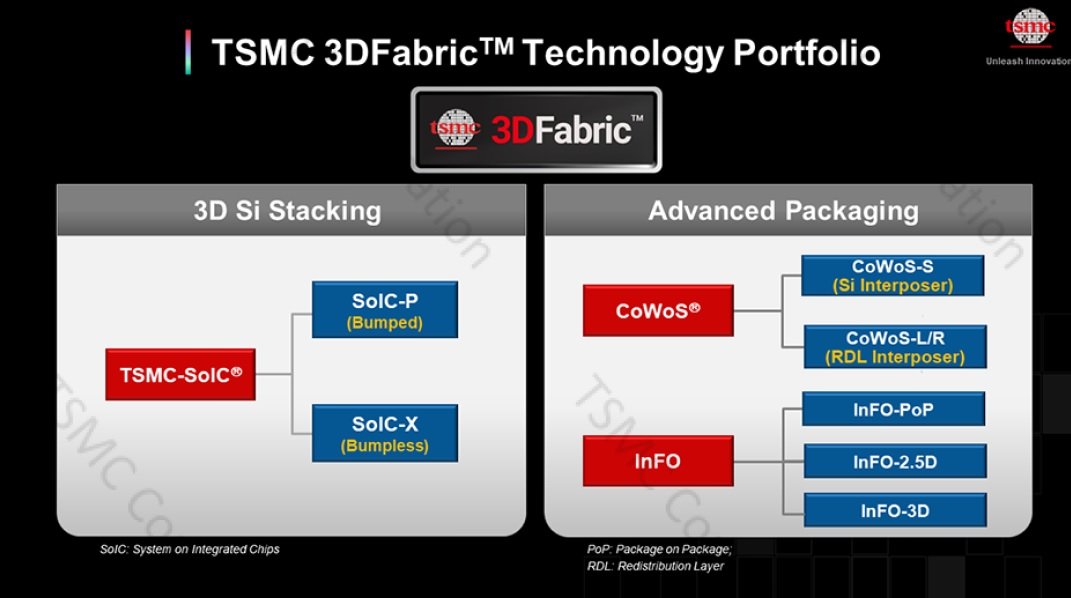

为了进一步发展微缩技术,以在单芯片片上系统(monolithic SoCs)中实现更小且更优异的晶体管,台积电还在开发3DFabric技术,通过发挥异质整合的优势,将系统中的晶体管数量提高5倍,甚至更多。3DFabric系统整合技术包括各种先进的3D芯片堆叠和先进封装技术,以支持广泛的下一代产品,包括:oyqesmc

在3D芯片堆叠方面,通过在系统整合芯片(TSMC-SoIC®)技术家族中加入微凸块的SoIC-P,得以支持更具成本敏感度的应用。oyqesmc

2.5D CoWoS平台实现先进逻辑和高频宽记忆体的整合,适用于人工智能、机器学习和数据中心等HPC应用;整合型扇出层叠封装技术(InFO PoP)和InFO-3D支持移动应用,InFO-2.5D则支持HPC小芯片整合。oyqesmc

基于堆叠芯片技术的系统整合芯片(SoIC)现可被整合于整合型扇出(InFO)或CoWoS封装中,以实现最终系统整合。oyqesmc

oyqesmc

oyqesmc

1. CoWoS®家族oyqesmc

主要针对需要整合先进逻辑和高带宽存储器的 HPC 应用。目前已经支持超过 25 个客户的140多种CoWoS产品。oyqesmc

所有CoWoS解决方案的中介层面积均在增加,以便整合更多先进芯片和高带宽存储器的堆叠,以满足更高的性能需求。oyqesmc

台积公司正在开发具有高达6个光罩尺寸(约5,000 平方毫米)重布线层(RDL)中介层的CoWoS解决方案,能够容纳 12 个高带宽存储器堆叠。oyqesmc

2. InFO工艺技术oyqesmc

在行动应用方面,InFO PoP自2016年开始量产并运用于高端移动设备,可以在更小的封装规格中容纳更大、更厚的系统级芯片(SoC)。oyqesmc

在 HPC 应用方面,无基板的InFO_M支持高达500平方毫米的小芯片整合, 适用于对外型尺寸敏感度较高的应用。oyqesmc

3. 3D芯片堆叠技术oyqesmc

SoIC-P采用18-25微米间距微凸块堆叠技术,主要针对如移动、物联网等成本较为敏感的应用。 oyqesmc

SoIC-X采用无凸块堆叠技术,主要针对HPC应用。其芯片对晶圆堆叠方案具有4.5至9微米的键合间距,已在台积公司的N7工艺技术中量产,用于HPC应用。oyqesmc

SoIC堆叠芯片可以进一步整合到CoWoS、InFo或传统倒装芯片封装,运用于客户的最终产品。oyqesmc

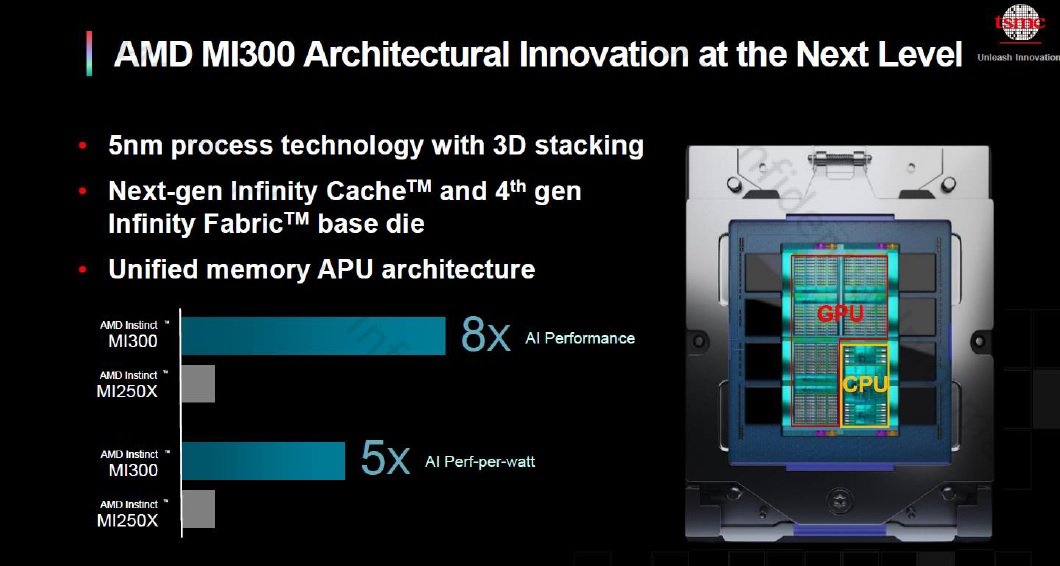

AMD成功展示了采用SoIC-X技术将N5 GPU和CPU堆叠于底层芯片,并整合在CoWoS封装中,以满足下一代百万兆级(exa-scale)运算的需求,这也是3DFabric技术推动HPC创新的代表性案例。oyqesmc

oyqesmc

oyqesmc

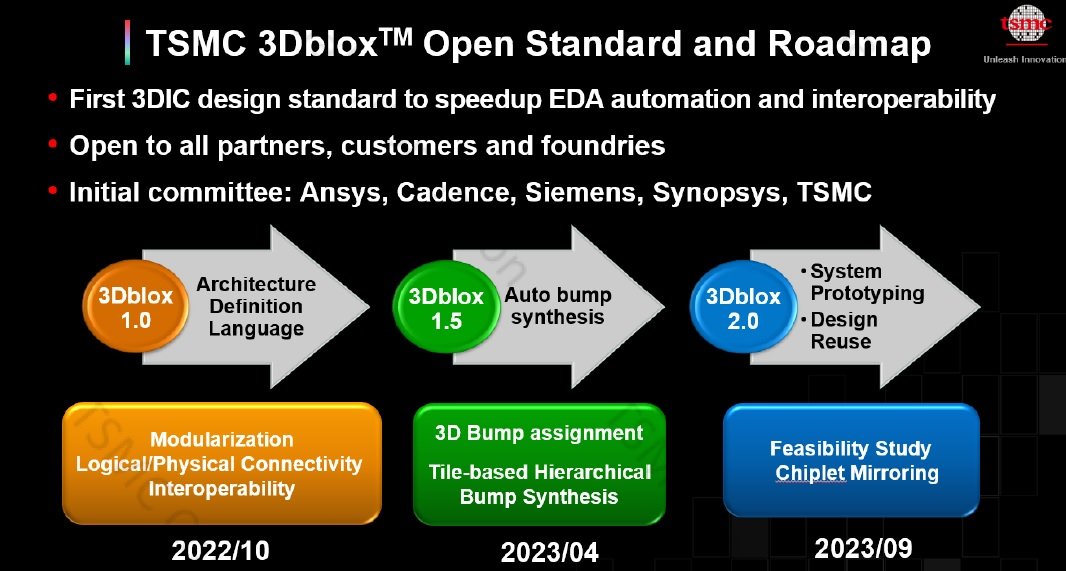

为了促进下一代HPC和移动设计的生态系统合作,在去年的开放创新平台(Open Innovation Platform,OIP)论坛上,台积电还宣布推出新的3DFabric™联盟,这也是继IP联盟、电子设计自动化(EDA)联盟、设计中心联盟(DCA)、云端(Cloud)联盟和价值链联盟(VCA)之后的第六个OIP联盟,具体包括:oyqesmc

— 提供3Dblox开放标准oyqesmc

— 实现存储器和台积公司逻辑工艺之间的紧密协作oyqesmc

— 将基板和测试合作伙伴导入生态系统oyqesmc

最新版本的开放式标准设计语言3Dblox™ 1.5,旨在降低3D IC设计的门槛。oyqesmc

oyqesmc

oyqesmc

特殊工艺

台积电特殊工艺包括电源管理、射频、CMOS影像感测等,涵盖广泛的应用领域。据透露,从2017年到2022年,台积电对特殊工艺技术投资的年复合增长率超过40%,预计到2026年,台积电特殊工艺产能提升近50%。oyqesmc

- 汽车

随着汽车产业向自动驾驶方向发展,运算需求正在快速增加,且需要最先进的逻辑技术。到2030年,台积电预计90%的汽车将具备先进驾驶辅助系统(ADAS),其中L1、L2和L2+/L3将有望分别达到30%的市场占有率。oyqesmc

过去三年里,台积电推出了汽车设计实现平台(ADEP),通过提供领先业界、Grade 1品质认证的N7A和N5A工艺来实现客户在汽车领域的创新。作为提前启动产品设计并缩短上市时间的垫脚石,Auto Early能够让客户在技术成熟前就能预先进行汽车产品设计。其中,N4AE是基于N4P开发的新技术,将允许客户在2024 年开始进行试产;N3AE则成为N3A的坚实基础,N3A将于2025年全面通过汽车制程验证,并将成为全球最先进的汽车逻辑工艺技术。oyqesmc

- 支持5G和联网性的先进射频技术

N6RF是台积电在2021年推出的7纳米逻辑工艺技术,在速度和能源效率方面均具有同级最佳的晶体管性能。客户可以通过从16FFC转换到N6RF,在半数字和半模拟的射频SoC上实现49%的功耗降低,减免移动设备在能源预算以支持其他不断成长的功能。oyqesmc

而最新的消息则是台积电宣布推出最先进的互补式金属氧化物半导体(CMOS)射频技术N4PRF,预计于 2023 年下半年发布。相较于N6RF,N4PRF逻辑密度增加77%,MOM电容密度增加了32%,在相同效能下功耗降低45%。oyqesmc

- 超低功耗

众所周知,Vdd对实现对电子产品的节能至关重要。因此,从55ULP 0.9V Vdd,到N6e 低于0.4V的Vdd,台积电提供广泛的电压操作范围,以实现动态电压调节设计来达成最佳的功耗∕性能。相较于N22解决方案,即将推出的N6e解决方案可提供约4.9倍的逻辑密度,并可降低超过70%的功耗,为穿戴式设备提供极具吸引力的解决方案。 oyqesmc

- MCU/嵌入式非挥发性存储器

目前,台积电最先进的eNVM技术已经发展到了基于16/12纳米的鳍式场效应晶体管(FinFET)技术,令客户能够从FinFET晶体管架构的优秀性能中获益。同时,由于传统的浮闸式eNVM或ESF3技术越来越复杂,台积电还在RRAM和MRAM等新型嵌入式存储器技术上加大了投资力度。这两种新技术都已经取得了成果,正在22纳米和40 纳米上投产,6纳米eNVM技术开发也在计划中。oyqesmc

RRAM方面,台积电28纳米RRAM进展顺利,具备可靠效能,适于汽车应用。40/28/22 纳米的RRAM已经于2022年第一季开始生产,下一代12纳米RRAM预计在2024 年第一季就绪。oyqesmc

2020年开始生产的22纳米MRAM主要用于物联网应用。现在,台积电正在与客户合作将MRAM技术用于未来的汽车应用,并预计在2023年第二季取得Grade 1汽车等级认证。oyqesmc

- CMOS影像感测

虽然智能手机的相机模组一直是互补式金属氧化物半导体(CMOS)影像感测技术的主要驱动力,但台积电预计车用相机将推动下一波CMOS影像感测器(CIS)的增长。为此,新的感测器架构,例如堆叠像素感测器、最小体积的全域快门感测器、基于事件的RGB 融合感测器,以及具有集成存储器的AI感测器,正成为台积电关注的重点。oyqesmc

- 显示器

下一代高阶OLED面板将需要更多的数字逻辑和静态随机存取存储器(SRAM)内容,以及更快的帧率,为了满足此类需求,台积电正在将其高压(HV)技术导入到28纳米的产品中,以实现更好的能源效率和更高的静态随机存取存储密度。而独有的µDisplay on silicon技术可以提供高达10倍的像素密度,以实现如AR和VR中使用的近眼显示器所需之更高分辨率。oyqesmc

强大的制造能力

为了满足客户不断增长的需求,台积电加快了晶圆厂拓展的脚步。从2017年到2019 年,公司平均每年进行大约2期的晶圆厂建设工程;从2020年到2023年,台积电晶圆厂的平均建设进度大幅增加至每年约5期。oyqesmc

在过去两年,台积电总共展开了10期的晶圆厂新建工程,包括在台湾地区的5期晶圆厂工程与2期先进封装厂工程,以及全球范围内的3期晶圆厂工程。oyqesmc

- 台湾地区以外,28纳米及以下工艺产能在2024年将比2020年增加3倍。在台湾地区,台积公司N3制程量产的基地在南科18厂;此外,台积公司正在为N2制程的新晶圆厂进行准备。

- 在中国大陆,南京厂新1期的28纳米制程晶圆厂已于2022年开始量产。

- 在美国,正在亚利桑那州建造2期晶圆厂。第一期已经开始移入设备,第二期正在兴建中。

- 在日本,台积公司正在熊本兴建一座晶圆厂,以提供16纳米和28纳米技术。

oyqesmc

oyqesmc

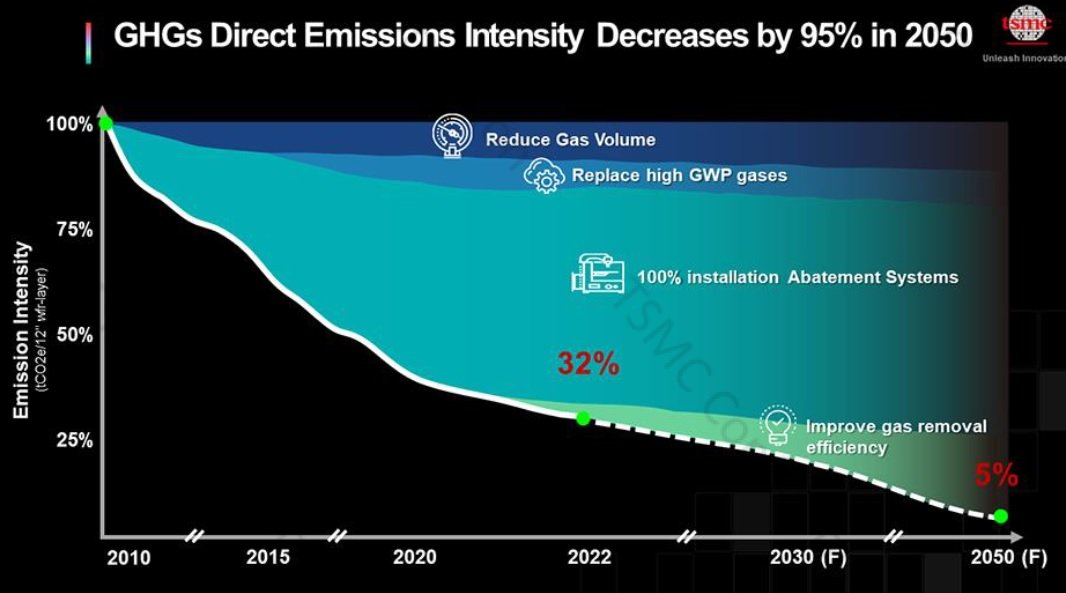

与此同时,台积电方面表示,为了实现2050年净零排放的目标,2022年,直接温室气体排放量已经较2010年降低了32%,该成果是通过降低工艺气体消耗、替换可能造成全球暖化的气体、安装现场废气处理设备,以及提高气体去除效率等方式实现的。oyqesmc

去年,台积电在台湾地区南部建立了第一座再生水厂,每日供水量5,000吨,时至今日,该再生水厂每日供水量达20,000吨。预计到2030年,台积电每生产单位自来水消耗量将降至2020年的60%。oyqesmc

接下来,台积电还将向着“每个工艺技术于量产第五年时,生产能源效率提高一倍”的目标前进。预计到2024年,N5制程技术的生产能源效率将比N7提高2.5倍。oyqesmc

-

微信扫一扫,一键转发

-

关注“国际电子商情” 微信公众号

- 韩国出口额创纪录,半导体成经济增长引擎

随着全球半导体需求的回暖,尤其是在内存芯片需求的持续推动下,韩国出口额实现连续15个月增长……

- 电子元件进出中国的关键:质量测试不可忽视

中国的电子元件产业在全球占据了重要地位。

- 供应链中假冒元件猖獗,靠AI就能解决问题吗?

通过在采购流程中引入人工智能,制造商得以精准预测市场需求、实时跟踪货物、有效评估潜在风险,并与供应商高效协调。提升透明度为制造商提供了更清晰的视野,有效助力他们缓解电子产品供应链中的假冒问题。

- 打造高效半导体供应链策略:消除浪费、持续改进、方针管

半导体行业是现代技术架构的基石,它为从智能手机到电动汽车等众多设备提供核心动力。从原材料硅晶圆到芯片成品,半导体产品的生产流程极其复杂,涵盖了众多阶段和利益相关方。在优化错综复杂的供应链的过程中,精益管理理念,包括消除浪费(Muda)、方针管理(Hoshin Kanri),以及持续改进(Kaizen),扮演着至关重要的角色。

- 如何解决电子垃圾难题?元器件制造商开“药方”

全球每年产生6,000万吨以上的电子垃圾,其中不到四分之一被回收再利用。

- 供应链管理创新策略:应对电力波动,确保订单时效

电力波动,无论是短暂的电压骤降、电流浪涌,还是持续性的停电,均可能对生产流程、库存管理和物流运作造成严重干扰。这些电力不稳定现象可能导致设备损坏、数据丢失,以及生产计划受阻,进而削弱供应链的整体可靠性和效率。

- OEM如何管理半导体过时问题?

当半导体更新换代的速度与终端产品长期的耐用性需求产生显著差异时,电子产品原始设备制造商(OEM)必须与其供应商紧密合作,共同策划并保障关键半导体部件的持续供应,以满足市场需求和产品的长期稳定运行。

- 供应链警钟:制造商常犯的三大错误

芯片供应链的脆弱性还在凸显,这促使制造商积极采取措施,以防范类似危机再次发生。

- MLCC卖不动了?主流厂商动向如何?

中国汽车市场正经历车用级MLCC产品的价格战

- 多重因素推动被动器件需求,风华高科如何抓住机遇?

被动元器件的价格经过前几年的波动之后,到2024年上半年处于相对稳定的状态。在这种情况下,厂商挖掘新的业绩增长点且持续关注市场新机遇,是决定未来能否跟上行业发展的关键因素。

- GPU之后,AI算力加速找到新方向

种种迹象表明,得益于自身对神经网络计算进行的专门优化,在端侧和边缘侧处理复杂神经网络算法时拥有的更高效率和更低能耗,神经网络处理器(NPU)正成为推动AI手机、AI PC和端侧AI市场前行的强大动能,并有望开启属于自己的大规模商用时代。

- “1龙”+“3虎”:分销行业头部格局或初现

明年,全球分销商TOP50强的座次究竟如何变化,让我们拭目以待!

- 全球半导体设备市场,方兴未艾!

近日,Tokyo Electron(以下简称“TEL”)宣布,将在日本宫城县建造一座新的生产大楼,由TEL的制造子公司TEL宫城公司

- 中国北大研究团队,氮化镓技术获新进展

近日,北京大学物理学院杨学林、沈波团队,联合宽禁带半导体研究中心等多个科研机构,在氮化镓外延薄膜中位错的原

- 2025年数据中心五大趋势

数据中心/云计算可以说是人工智能领域的核心,占据了英伟达总收入的85%~90%。

- 重庆发布新政,聚焦高端芯片与器件发展

近日,重庆市人民政府办公厅印发《重庆市推动经济持续向上向好若干政策举措》,提出支持科技领军企业、产业链龙

- 消息称苹果取消Mac连接AR眼镜,独立AR眼镜研发仍推进中

2月10日消息,据彭博社记者马克·古尔曼报道,苹果公司取消了一款与Mac连接使用的AR眼镜项目,但仍在积极推进独立

- 三星2nmSF2工艺试产良率约30%?

韩国媒体TheBell报道,三星正在为旗下自研处理器Exynos2600投入大量资源,以确保其按时量产。

- 2024年Q4平板电脑市场整体增长放缓,iPad占据40%市场份额

尽管全球平板电脑市场在2024年的大部分时间都保持着两位数的增长,但在2024年Q4,平板电脑出货量仅同比增长3%。

- AR微显示厂商Cellid完成1300万美元融资

2月7日,日本AR眼镜光学厂商Cellid宣布,公司通过定向增发完成总额1300万美元(约人民币9478.95万元)的融资。

- 多家半导体大厂官宣换帅!

近日,多家媒体发布消息称,瑞芯微前副总经理陈锋将出任Arm在中国的合资公司安谋科技首席执行官(CEO)一职。

- 全球半导体厂商营收10强排行榜出炉!

美国市场研究机构Gartner发布2024年全球半导体厂商营收排行榜。

- 2024年先进封装晶圆占比近半

随着传统扩展方式的成本和复杂性上升,先进封装已成为满足人工智能(尤其是大型语言模型训练)性能需求的一种方式

- 2024年AIPC未能提振笔电市场,仅从2023年的低点温和增长5%

2024年Q4,全球笔记本电脑出货量同比增长了6%,达到5450万台。

- 英飞凌在泰国新建后道工厂,优化和丰富生产布局

英飞凌位于曼谷南部沙没巴干府的新后道厂破土动工,该厂将扩大公司在亚洲的生产布局。

- 芯耀辉:从传统IP到IP2.0,AI时代国产IP机遇与挑战齐飞

2024年,集成电路行业在变革与机遇中持续发展。面对全球经济的新常态、技术创新的加速以及市场需求的不断变化

- 艾睿电子与印尼初创协会合作,支持本地科技初创公司

雅加达,印尼- 2025年1月14日 - 全球技术解决方案供应商艾睿电子(Arrow Electronics)与印尼初创协会合作(STARFIN

- 【凯新达科技】新年欢聚,共绘年会精彩篇章!

无畏挑战 共创未来祥龙回首留胜景,金蛇起舞贺新程。在2025年元旦新年之际,深圳市凯新达科技有限公司(以下简

- CES 2025新品:摩尔斯微电子推出Wi-Fi芯片MM8108

最新Wi-Fi HaLow片上系统(SoC)为物联网的性能、效率、安全性与多功能性设立新标准;

配套USB网关,轻松实现Wi- - ST与彭水共绘可持续发展新篇章

随着与三安光电的碳化硅合资工厂落地重庆,2024年6月,意法半导体与重庆市彭水自治县同步启动了可持续发展合作

- 【凯新达科技】2025年度旅游活动景点精彩报道

凯新达科技 自由之旅 征途同行

- 超高性价比AI电脑:英伟达NVIDIA Jetson Orin Nano Super真香!iCEas

NVIDIA Jetson Orin™ Nano Super 开发者套件是一款尺寸小巧且性能强大的超级计算机,重新定义了小型边

- TI推出新一代支持边缘AI的雷达传感器和汽车音频处理器,改进车内驾

德州仪器今日推出了全新的集成式汽车芯片,能够帮助各个价位车辆的驾乘人员,实现更安全、更具沉浸感的驾驶体验

- 【原厂入驻】飞虹半导体现已入驻iCEasy商城!

广州飞虹半导体科技有限公司成立于广州越秀区,诚信经营20多年。主要研发、生产、经营:场效应管、三极管等半

- 携手共进,江波龙与电子五所在中山展开深度交流

近日,半导体存储品牌企业江波龙与工业和信息化部电子第五研究所(中国赛宝实验室,以下简称“电子五所”)在江波龙

- 【原厂入驻】迈巨微电子现已入驻iCEasy商城!

深圳迈巨微电子有限公司深耕锂电池管理芯片领域,围绕电池健康和安全,电池电量计算二个核心技术能力,提供完善的