都是7纳米,台积电、三星、英特尔和中芯国际的有什么不同?

2023-09-05 17:34:34

7纳米,这个数量词一夜间因为华为Mate 60系列的发布,再度映入人们的眼帘。

之所以说是“再度”,是因为对全球半导体顶尖玩家来说,7nm已经是2018/2019年的事情了,而对我们来说,全面量产之路似乎才刚刚开始。不过,也正好借这个机会,梳理对比一下台积电、三星、英特尔和中芯国际各自7nm工艺的差异和演进路线,做到“温故知新,心中有数。”eGFesmc

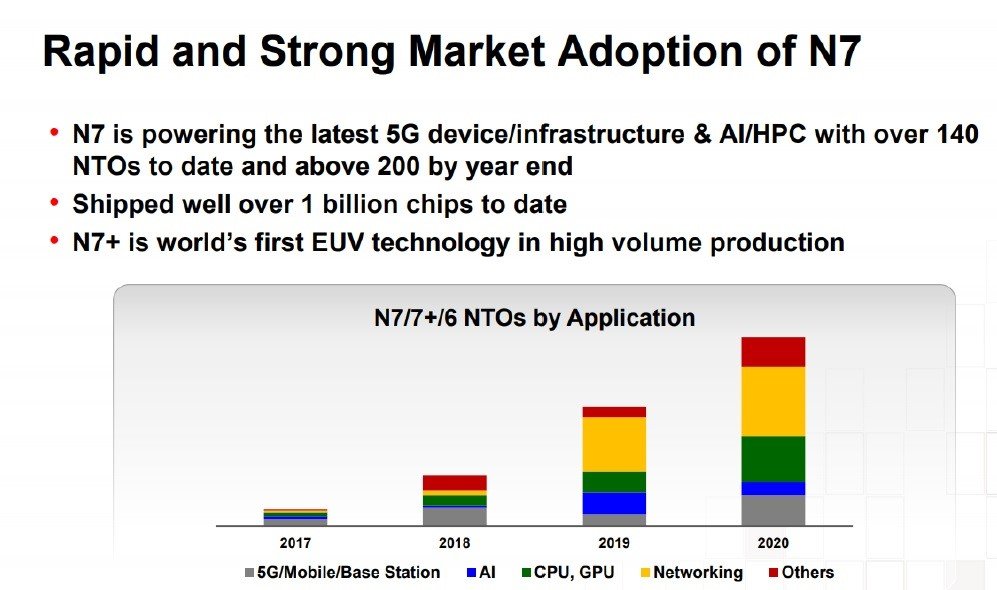

台积电早在2017年就率先进入7nm时代,并从2018年4月开始大规模量产,N7产品采用DUV(深紫外光)193nm浸没式ArF技术,栅极间距57nm,标准单元高度为6 Track,被广泛地应用在了高通骁龙855、苹果A12、华为海思Kirin 990、AMD Zen 2这些SoC产品上。到2020年底,台积电在7nm节点上就获得了超过200个新产品流片(NTO),累计生产7nm芯片超过10亿颗。eGFesmc

eGFesmc

eGFesmc

从WikiChip分享的信息来看,台积电的N7工艺有两种Cell方案,分别对应低功耗与高性能,其中,低功耗N7每平方毫米百万晶体管为91.2(即91.2MTr/mm²),高性能N7每平方毫米百万晶体管为65(即65MTr/mm²)。eGFesmc

随后,台积电又推出了得到苹果A13和骁龙865使用的N7P工艺,以及使用EUV(极紫外线)技术的N7+工艺。按照台积电的说法,得益于4层EUV工艺,N7+有着1.2倍的晶体管密度提升,相同功耗下提升10%性能,相同性能下降低15%功耗,当时的海思Kirin 990 5G版芯片也因此获益。eGFesmc

N7之后,2019年下半年,台积电又推出了与7nm工艺平台完全兼容的6nm工艺,一方面希望用更先进的工艺来实现更高的逻辑密度,另一方面又便于客户很容易的将7nm设计移植到6nm平台之上。数据显示,N6平台在逻辑密度方面的提升接近20%。eGFesmc

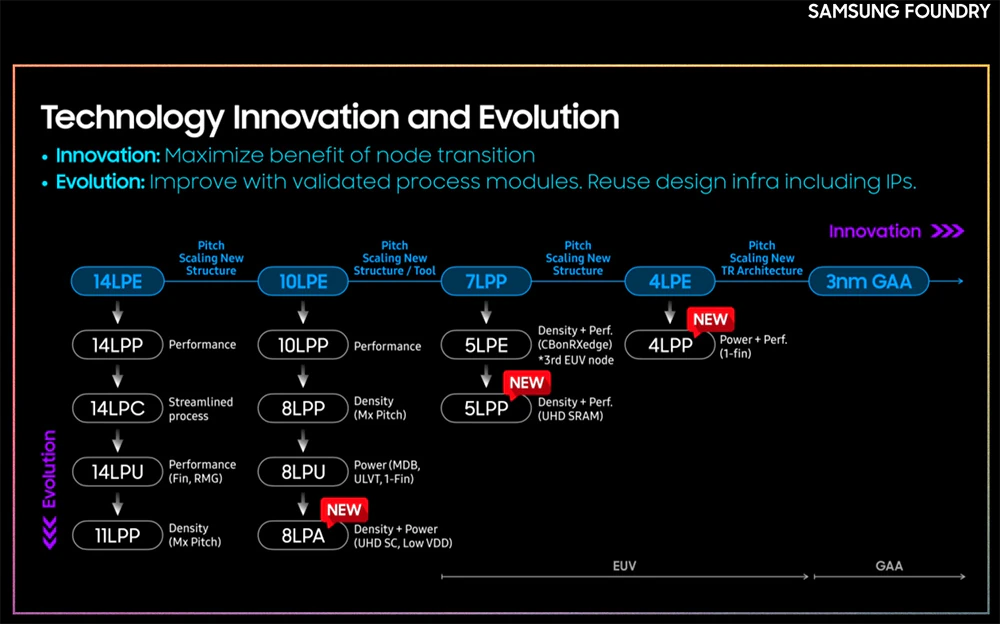

三星当时在7nm工艺上走的更加激进,直接采用了EUV技术。新工艺减少了20%的光罩流程,另外还达成40%面积缩小、20%性能增加与55%的功耗降低目标。此外,EUV的加入还带来了更高的图案保真度、更紧致的关键尺寸分布等特性。但很遗憾,目前为止,EUV还是我们的“卡脖子”的领域。eGFesmc

WikiChip的数据显示,三星7nm LPP HD高密度cell方案的晶体管密度在95.08 MTr/mm²,而HP高性能方案的晶体管密度则在77.01 MTr/mm²,总体感觉是相比台积电N7工艺略有优势,但不及同样用上了EUV的N7+。eGFesmc

eGFesmc

eGFesmc

2020年公布的三星foundry工艺演进路线eGFesmc

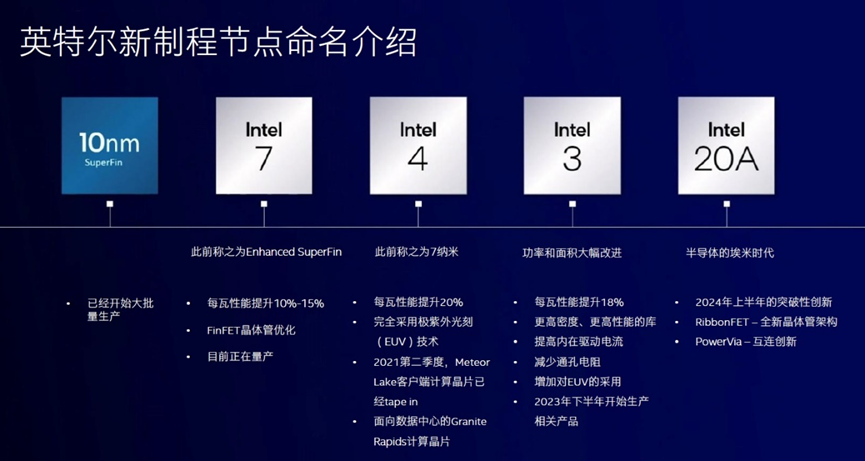

2021年,英特尔认为基于纳米的传统制程节点命名方法,不再与晶体管实际的栅极长度相对应,为此引入了全新的制程节点命名体系。eGFesmc

按照当时的规划,此前被称之为7纳米的工艺改称Intel 4,完全采用EUV光刻技术,可使用超短波长的光,刻印极微小的图样。凭借每瓦性能约20%的提升以及芯片面积的改进,Intel 4在2022年下半年投产,并于2023年出货,这些产品包括面向客户端的Meteor Lake和面向数据中心的Granite Rapids。eGFesmc

eGFesmc

eGFesmc

目前关于中芯国际7纳米的资料不多,一些已知的消息显示,SMIC N+1 7nm技术最早之前用于MinerVA7 Bitcoin Miner ASIC应用,产量较小,在典型的逻辑电路中引入更高Vt值晶体管是亮点之一。之后,为了降低工艺复杂性和提高产量,中芯国际还引入了一些协同优化技术,可能会用于后续工艺节点。eGFesmc

但不管怎样,台积电从16nm到10nm再到7nm,用了3年时间;三星从14nm到10nm再到7nm用了5年时间,而中芯国际仅用2年时间就取得了7nm的成就,而且还是在无法获得西方先进设备和技术的情况下,为建立完全国内先进的SoC设计和制造生态系统打开了大门,是一件值得骄傲的事情。eGFesmc

微信扫一扫,一键转发

关注“国际电子商情” 微信公众号

近日,Tokyo Electron(以下简称“TEL”)宣布,将在日本宫城县建造一座新的生产大楼,由TEL的制造子公司TEL宫城公司

近日,北京大学物理学院杨学林、沈波团队,联合宽禁带半导体研究中心等多个科研机构,在氮化镓外延薄膜中位错的原

数据中心/云计算可以说是人工智能领域的核心,占据了英伟达总收入的85%~90%。

近日,重庆市人民政府办公厅印发《重庆市推动经济持续向上向好若干政策举措》,提出支持科技领军企业、产业链龙

2月10日消息,据彭博社记者马克·古尔曼报道,苹果公司取消了一款与Mac连接使用的AR眼镜项目,但仍在积极推进独立

韩国媒体TheBell报道,三星正在为旗下自研处理器Exynos2600投入大量资源,以确保其按时量产。

尽管全球平板电脑市场在2024年的大部分时间都保持着两位数的增长,但在2024年Q4,平板电脑出货量仅同比增长3%。

2月7日,日本AR眼镜光学厂商Cellid宣布,公司通过定向增发完成总额1300万美元(约人民币9478.95万元)的融资。

近日,多家媒体发布消息称,瑞芯微前副总经理陈锋将出任Arm在中国的合资公司安谋科技首席执行官(CEO)一职。

美国市场研究机构Gartner发布2024年全球半导体厂商营收排行榜。

随着传统扩展方式的成本和复杂性上升,先进封装已成为满足人工智能(尤其是大型语言模型训练)性能需求的一种方式

2024年Q4,全球笔记本电脑出货量同比增长了6%,达到5450万台。

英飞凌位于曼谷南部沙没巴干府的新后道厂破土动工,该厂将扩大公司在亚洲的生产布局。

2024年,集成电路行业在变革与机遇中持续发展。面对全球经济的新常态、技术创新的加速以及市场需求的不断变化

雅加达,印尼- 2025年1月14日 - 全球技术解决方案供应商艾睿电子(Arrow Electronics)与印尼初创协会合作(STARFIN

无畏挑战 共创未来祥龙回首留胜景,金蛇起舞贺新程。在2025年元旦新年之际,深圳市凯新达科技有限公司(以下简

最新Wi-Fi HaLow片上系统(SoC)为物联网的性能、效率、安全性与多功能性设立新标准;

配套USB网关,轻松实现Wi-

随着与三安光电的碳化硅合资工厂落地重庆,2024年6月,意法半导体与重庆市彭水自治县同步启动了可持续发展合作

凯新达科技 自由之旅 征途同行

NVIDIA Jetson Orin™ Nano Super 开发者套件是一款尺寸小巧且性能强大的超级计算机,重新定义了小型边

德州仪器今日推出了全新的集成式汽车芯片,能够帮助各个价位车辆的驾乘人员,实现更安全、更具沉浸感的驾驶体验

广州飞虹半导体科技有限公司成立于广州越秀区,诚信经营20多年。主要研发、生产、经营:场效应管、三极管等半

近日,半导体存储品牌企业江波龙与工业和信息化部电子第五研究所(中国赛宝实验室,以下简称“电子五所”)在江波龙

深圳迈巨微电子有限公司深耕锂电池管理芯片领域,围绕电池健康和安全,电池电量计算二个核心技术能力,提供完善的

点击查看更多

北京科能广告有限公司深圳分公司 版权所有

分享到微信

分享到微博

分享到QQ空间

推荐使用浏览器内置分享

分享至朋友圈