泰瑞达:美国技术含量低于3%,推动国产IC实现零缺陷目标

随着芯片制程缩小、晶体管密度增高,芯片复杂度及集成度呈指数级增长,而在芯片制程演进的过程中,测试设备也面临着诸多挑战。

实际上,不仅是芯片制程工艺在升级,其对检测设备的要求也在升级。好的检测方案可帮助芯片公司,更早发现有缺陷的芯片,从而节省芯片生产的成本。在芯片设计日趋复杂、功能不断优化的趋势下,自动测试设备(ATE)提供商是如何满足各种芯片测试的需求的?3svesmc

日前,泰瑞达亚太区销售副总裁Richard Hsieh和泰瑞达中国区总经理黄飞鸿(Felix Huang)以芯片测试助力“汽车芯片实现零质量缺陷目标”为例,分享了“如何利用先进的测试解决方案减少缺陷逃逸、降低报废成本,并通过设计-制造-测试闭环实现良率目标”的话题,强调了完善的芯片测试方案对降低芯片生产成本、提升芯片良率的重要意义。3svesmc

3svesmc

3svesmc

测试设备伴随芯片迭代而不断升级

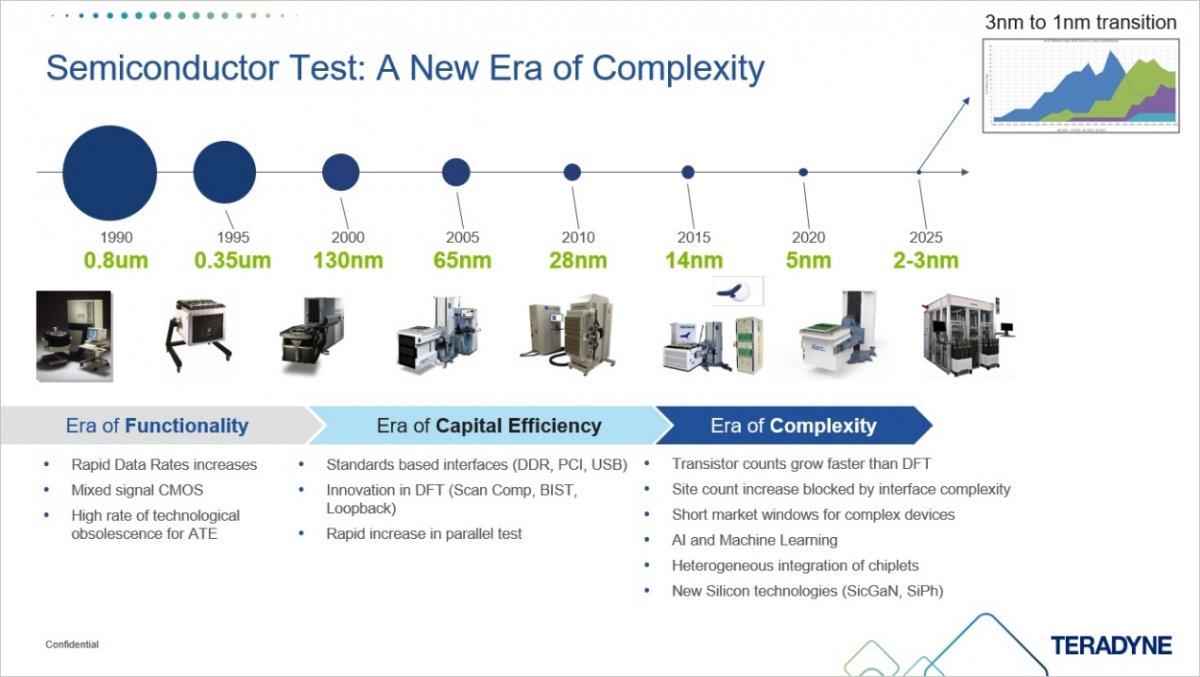

在过去三十余年里,芯片的制程从1990年的0.8μm工艺(英特尔50MHz 486微处理器),一路演进到现在的2nm、3nm工艺,未来还将向1nm制程演进。芯片制程的演进也带来了很多新挑战——尤其在功能部分,要求测试速度越来越快,同时芯片设计也越来越复杂。3svesmc

“不同的芯片在设计方面,可能会采用不同的制程,在CMOS的制程里制造数字芯片或‘数字+混合信号+RF’芯片,其实是一个很大的挑战。”Richard解释说,因为不同的芯片设计和制造工艺,可能会有不同的特点和要求,所以EDA设计需考虑到这些差异,并为之做出相应的调整。但由于EDA工具的功能存在一定的局限性,无法完全满足所有设计和制造工艺的需求,这就需要它在功能方面不断改进和优化。3svesmc

在芯片设计和制造过程中,测试设备用于检测和评估芯片的性能、功能和可靠性。由于不同的设计和制程工艺,可能会产生不同的芯片特性,针对不同的芯片类型和制造工艺,测试设备也要进行调整和优化。为了更好地满足芯片测试的需求,测试设备升级的周期也在缩短。3svesmc

泰瑞达1995年推出的J750围绕数字板卡的密度、电源模块等已经了三代。黄飞鸿介绍说:“之前每5-6年迭代一次SoC平台、每6-7年升级一代板卡,现在的升级周期缩短到3-4年。而泰瑞达2019年推出的UltraFLEXplus,其设计的生命周期是20年,每五年做一次小升级,并且始终保持开发软件全兼容。”3svesmc

令人十分惊喜的是,一些客户仍在使用泰瑞J750来测试量产的芯片。黄飞鸿解释道,J750最初设计的指标范围覆盖比较广,能满足国产MCU的测试指标,同时车规MCU更强调测试稳定性,J750经过20多年的迭代,已经具备极好的稳定性,所以这款产品才能使用这么久。3svesmc

一般来说,测试设备的稳定性可通过MTBF(Mean Time Between Failure,平均无故障时间)指标来确定,也即是“在满负荷不停机运行的情况下,设备板卡两次失效之间的平均时间”,而J750可连续无故障运行8760个小时,其稳定性超过其他测试设备。3svesmc

在谈到国产化相关的话题时,黄飞鸿也指出,泰瑞达在中国的策略是:扎根中国、服务中国。虽然泰瑞达是美国独资公司,但是它在中国已经扎根了20余年,在中国是一直是本土化的企业。据悉,在过去3年里,泰瑞达支持本土芯片企业的工程团队已突破60人。“其实我们所有的测试设备的美国成分都远低于3%,甚至一些设备的美国技术含量在1%左右,所以在合规性方面不存在问题。”3svesmc

另外,对芯片测试设备投资而言,资产是否能有效运用也很重要。测试产业是一个重资本投资的产业,要把测试设备的利用率设计得更高,能检测更多采用不同技术的芯片,且可维持很长的产品生命周期,才能取得更好的投资回报率。Richard以芯片测试为例指出,可通过增加“同测数”来降低成本,但这会让接口设计更复杂,也是影响芯片上市的原因之一,对此泰瑞达已经提前考虑到并且提供了高质量的解决方案。3svesmc

在测试先进工艺芯片时,会出现很多的测试数据,如何去分析、应用这些数据,助力提升芯片设计和量产良率,也是测试厂商当下面临的挑战。泰瑞达的解决方案是:采用软硬件结合的方式,从芯片设计环节开始,就参与进来做测试策略,一直到最后的系统端测试,全程参与不同环节的测试,最终帮助客户提升芯片良率。3svesmc

助力国产汽车芯片实现“零缺陷”目标

汽车行业对半导体的带动,主要受电动化、智能化两大因素驱使。根据S&P Global Mobility数据显示:2023年平均每辆车使用的半导体器件的金额为800-1000美金,预计2028年该数字将提升到1500美金。中国作为全球最大的新能源汽车市场,在该国聚集着许多车规级芯片供应商,也有许多芯片测试的需求。因此,对ATE厂商来说,中国充满着大量的市场机会。3svesmc

相比于普通的消费类芯片,车规芯片有更严格的质量要求,其目标是“零质量缺陷(0 DPPM,即每百万件不合格品为零)”。同时,汽车行业的不同环节也有不同的质量标准,比如针对芯片设计有AECQ100标准,针对全功能有ISO-26262安全功能要求,针对工厂有IATF16949认证……黄飞鸿强调说,任何一个环节都不能掉链子,哪怕出错率只有万分之一,但不同环节的出错率相乘之后,最终也会导致很大的质量缺陷。3svesmc

·灵活的测试平台可降低测试成本

3svesmc

3svesmc

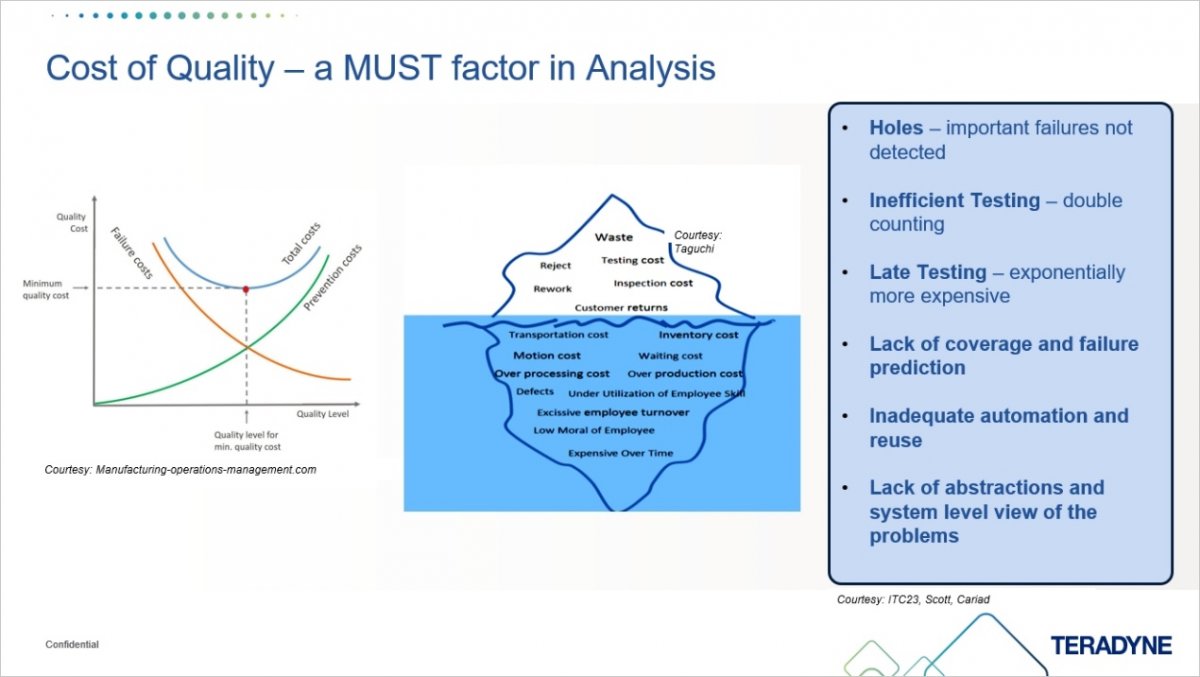

追求“零质量缺陷”也会带来更多的成本。如上图最左边的趋势图显示,横坐标代表质量等级,纵坐标代表成本,红色线条代表“质量等级越高,器件的失效成本就越低”,绿色线条体现“追求高质量也会额外增加成本”,这就需要做预防性的提前检测。红绿线的交界点是蓝色线条,其最低点是达到最小质量成本前提下的甜蜜点(Honey point)。不同功能的车规芯片来说,比如ADAS芯片、自动驾驶芯片、智能驾舱芯片、MCU控制芯片、传感器等,它们的标准和成本都不一样。3svesmc

上图右边部分列举了测试车规芯片时可能会遇到的一些问题,包括:重要的故障没有被检测到;重复计算导致非常低效的测试;无法尽早发现问题,等后续发现问题时,成本已呈指数级增长;芯片测试的自动化程度不足,并且缺乏重复使用的机会;对问题缺乏抽象和系统级别的理解。在设计测试方案和策略的初期阶段,就需要考虑到避免以上所有问题的出现。3svesmc

此外,随着汽车的算力在增加,其芯片的集成度也在提高。很多汽车业内人士认为,汽车芯片技术的主流将朝着Chiplet和异构集成发展。黄飞鸿坦言,这种趋势也给ATE厂商带来了更大的挑战。Chiplet又称芯粒或者小芯片,它是将一类满足特定功能的Die(裸片),通过Die-To-Die内部互联技术,实现多个模块芯片与底层基础芯片封装在一起,形成一个系统芯片,以实现一种新形式的IP复用。3svesmc

“Chiplet在把不同功能/工艺的模块封装在一颗芯片中,这省掉了一些工艺方面的花费。但它给ATE厂商带来的难题在于——‘如何检测Chiplet内部不同Die’。Chiplet中的不同Die之间在互连时,并非所有的管脚都放在壳体外,也意味着无法测试到内部所有的Die。这需要芯片设计公司来完善Chiplet的标准,进一步确定管脚的摆放问题。”3svesmc

目前,ADAS芯片的要求是10 DPPM,即每百万件不合格品为10,要达到车规要求的“零质量缺陷”,是一件相当困难的事。ATE要从前到后全链路覆盖,对芯片进行多环节的筛选,比如晶圆阶段的检测、PCB板的检测,以及上系统板后整个芯片功能的检测等。3svesmc

具体来看,ATE厂商在设计芯片时,就要考虑好从设计到量产的全部流程;在实现流程的过程中,要考虑如何多人、多步骤协作,这一切尽可能自动化;还要考虑是否有可靠的工具,来做实时性、可预测性、智能性的分析。以上所有环节都需要大数据的支撑。3svesmc

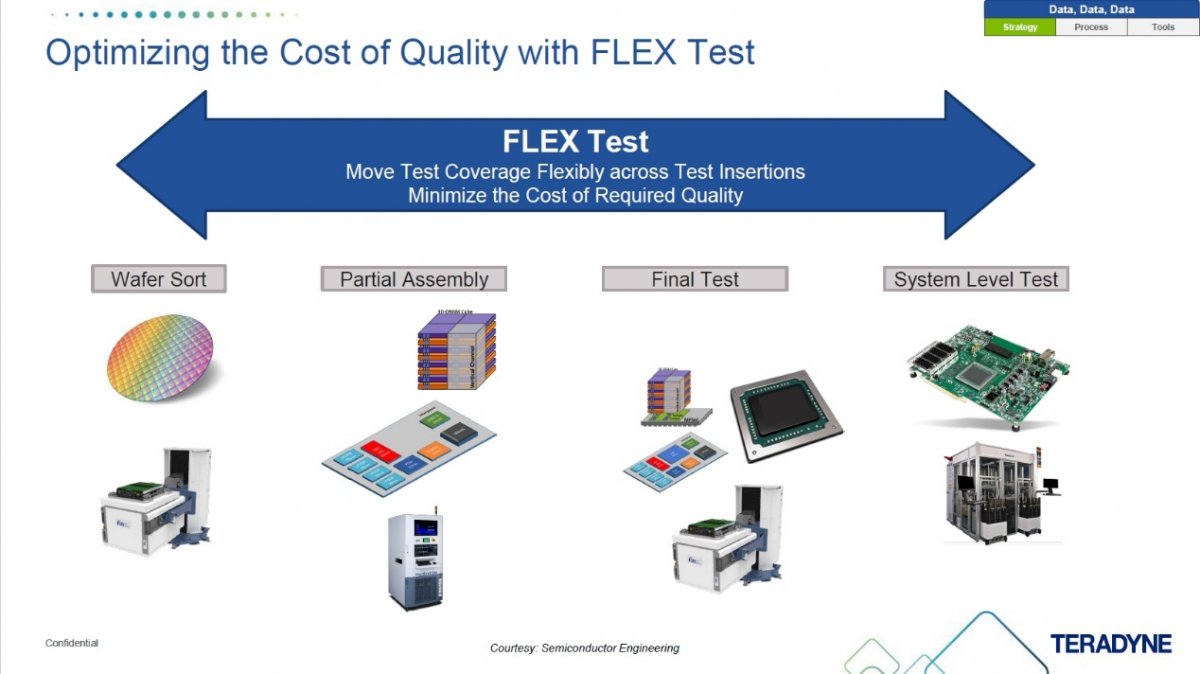

当然,即使通过了晶圆测试和成品测试,也不意味着测试流程的完结。因为以上两个阶段的测试项目,无法100%排除掉有问题的芯片,需把芯片安装到系统板上,只有通过了系统级测试才算结束。针对以上每一个测试环节,泰瑞达都能提供相应的服务。3svesmc

3svesmc

3svesmc

为了帮助企业最小化测试成本,泰瑞达还提供FLEX测试平台,如上图所示,该平台中的测试项目可前后移动。当芯片上的缺陷越早被发现,比如在晶圆测试阶段就检测出来,该芯片就不需要再进行成品测试,只需看封装可能导致的Die与Die互联带来的问题。与封装工艺成本相比,芯片的测试成本占比不大,越早发现问题就越节省封装成本。这要求检测设备具有非常好的稳定性、可重复性,测试能力和覆盖率能够达到相应的要求。“在整个流程中,要不断分析数据,只有分析完数据后,才知道哪些可往前移。想要在某个阶段测试更多芯片,就要在这一阶段配置更多的测试设备。”黄飞鸿表示。3svesmc

可能会有人好奇ATE行业的盈利模式。黄飞鸿分享道,“我们这个行业的盈利模式是销售设备。比如,台积电、SMIC等Fab,会购买我们的设备来测试晶圆。日月光、SPIL等OSAT厂,以及独立的测试厂,也会购买我们的设备,在芯片封装好后做测试。但测试厂购买什么设备由芯片设计公司决定,我们与芯片设计公司共同开发程序、设计芯片测试方案,后者会告诉测试工厂要采购多少台某款型号的设备,然后再付给测试厂相应的机时费(hour rate)。”3svesmc

·一系列工具集为提升芯片良率赋能

除了重资产的测试设备之外,泰瑞达还开发了一系列工具集,来助力设计人员在使用泰瑞达设备时,能尽早识别出有问题的芯片,从而提升芯片的良率。3svesmc

3svesmc

3svesmc

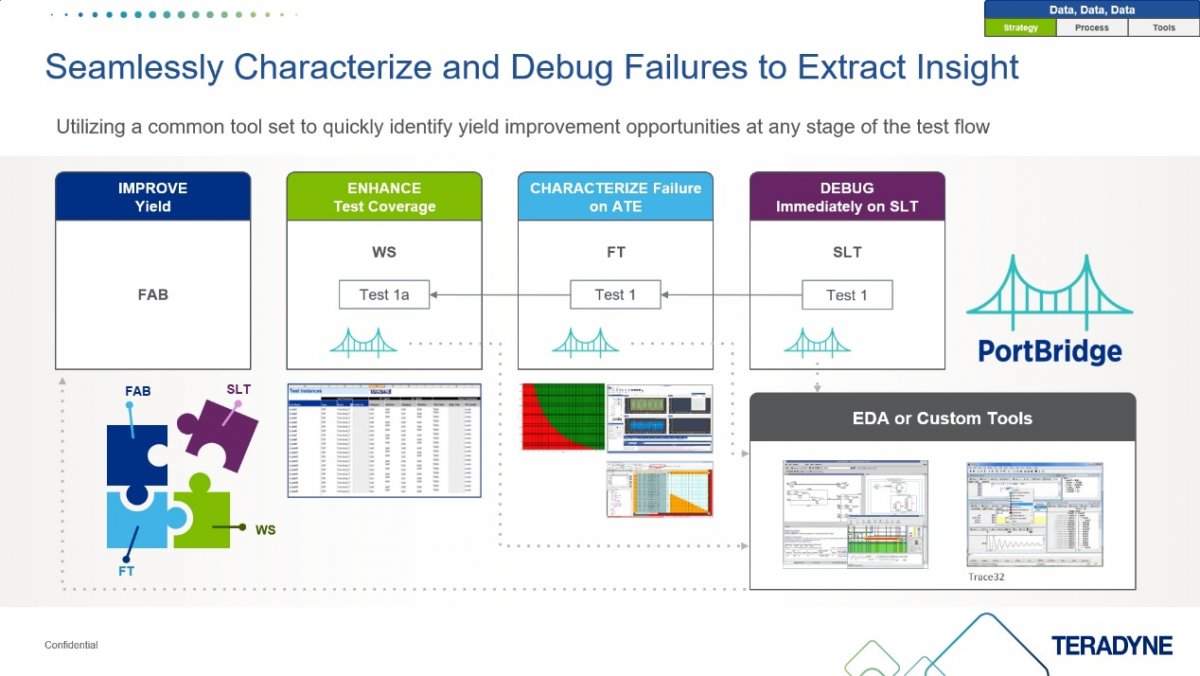

在测试策略阶段,泰瑞达有一个PortBridge软件,它是西门子EDA Tessent工具的界面接口。EDA的设计人员、DFT人员可通过PortBridge,用EDA工具直接连接泰瑞达的测试机,来控制晶圆测试、成品测试和系统端测试(SLT),并根据它们的结果实时在线做调试。3svesmc

在PortBridge软件诞生之前,定位芯片工艺缺陷的流程非常复杂。EDA公司的DFT设计人员,在调试某颗芯片时会生成一个WGL Pattern(一个可编辑的文本文件),再利用转换工具来转成ATE的向量,然后写成芯片测试程序,测试工程师根据测试程序调试这颗芯片,芯片调试结果出来后再转换成IC设计人员看得懂的格式,由IC设计人员来定位这个芯片失效是否与某个工艺流程有关。3svesmc

为此,泰瑞达与EDA公司Mentor Graphics合作开发了PortBridge软件,旨在帮助设计人员在初期阶段直接调试芯片,有助于FAB在早期阶段调试芯片良率。此外,PortBridge还能调试芯片IP,比如HDMI接口、LVDS接口、高速接口, IC设计人员可利用该软件,通过ATE来访问每个芯片IP,并对其进行调试,从而加速IP与芯片的融合。3svesmc

3svesmc

3svesmc

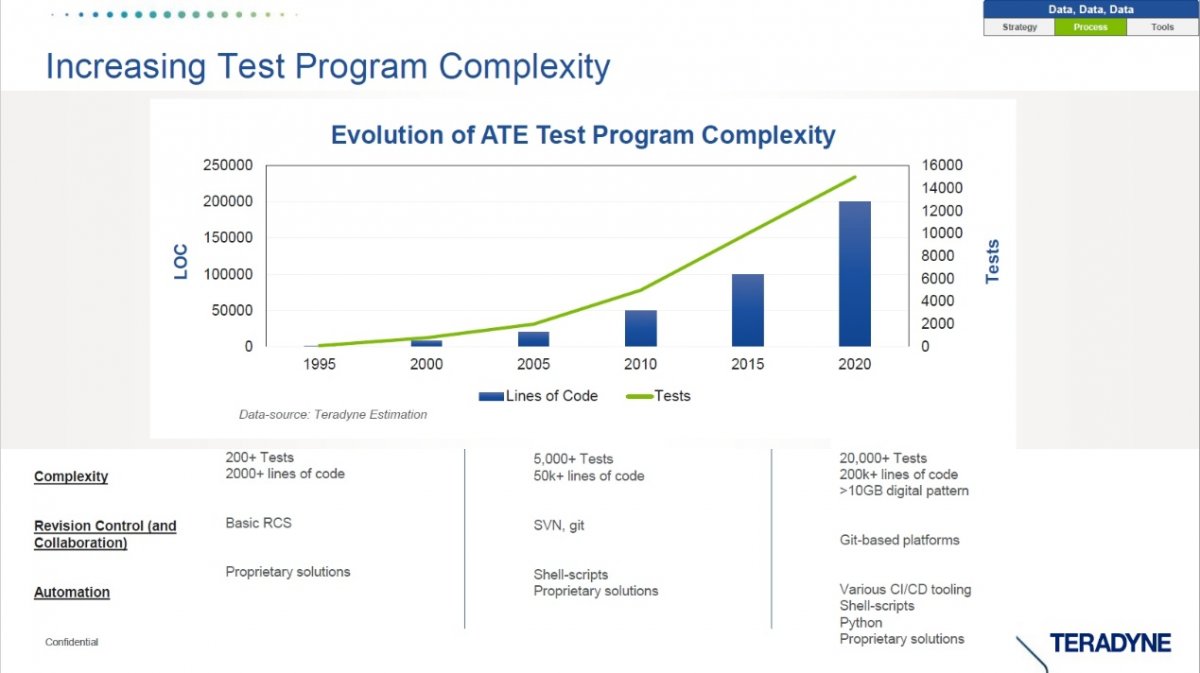

测试策略之后是测试程序阶段。芯片的功能在不断增加,导致芯片测试的代码量巨大。最早测量一颗芯片(SoC混合芯片),可能会有200个左右的测试项,约1000-2000行代码。现在的芯片测试项目有2万行,代码量达几个到十几个Giga。现在一般需要一个团队来开发测试程序,这对工具提出了自动化的要求。泰瑞达的测试程序开发基于IG-XL软件,基于该软件还有一个辅助工具Oasis,该工具可以检测开发的代码质量。比如在Offline(脱机)阶段运行Oasis工具,可自动检查代码有无错误和冗余。3svesmc

3svesmc

3svesmc

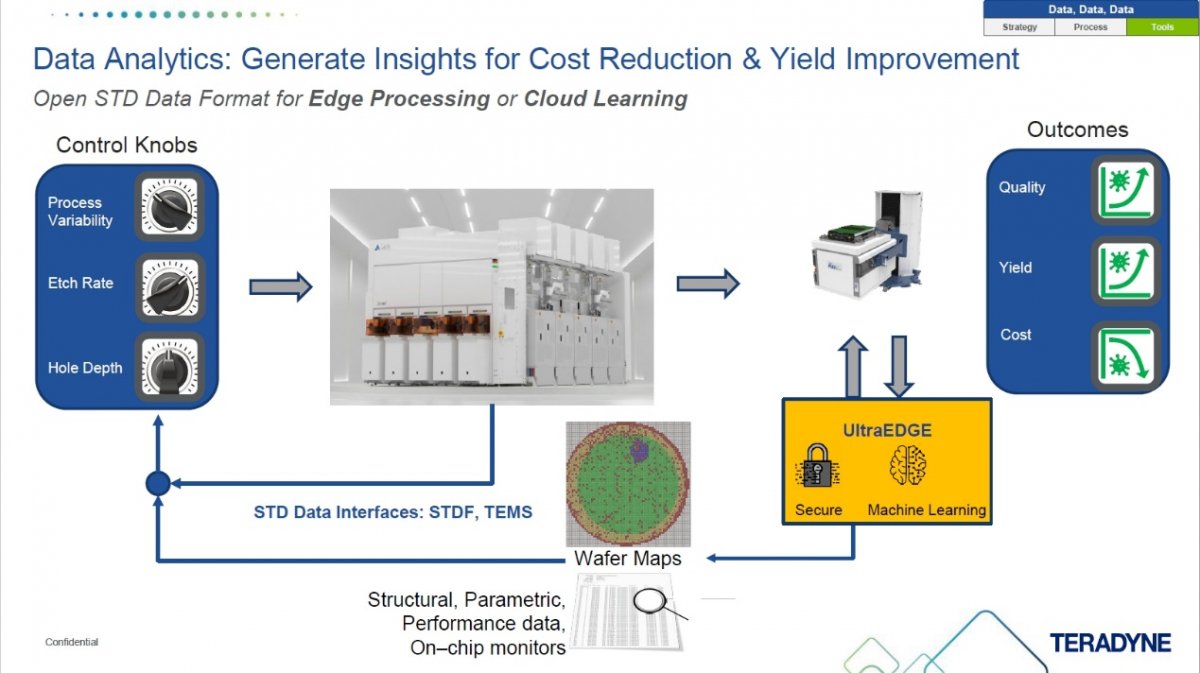

在黄飞鸿看来,数据分析是重中之重。上图中间的设备是刻蚀机,左边有不同的控制旋钮,旋钮有不同的变量/参数,蚀刻机右边是ATE测试晶圆,其中大量数据会通过UltraEDGE(一个服务器)做质量和数据统计,上面也可安装第三方数据分析软件,比如OptimalPlus、PDF数据管理软件等,在其中进行加密和机器学习,对抓到的原始数据进行分析,把潜在的缺陷问题体现出来,也可把数据反馈给Foundry。因此,共有两条途径来调整和改善工艺,其最终的目的是提升良率、降低成本。3svesmc

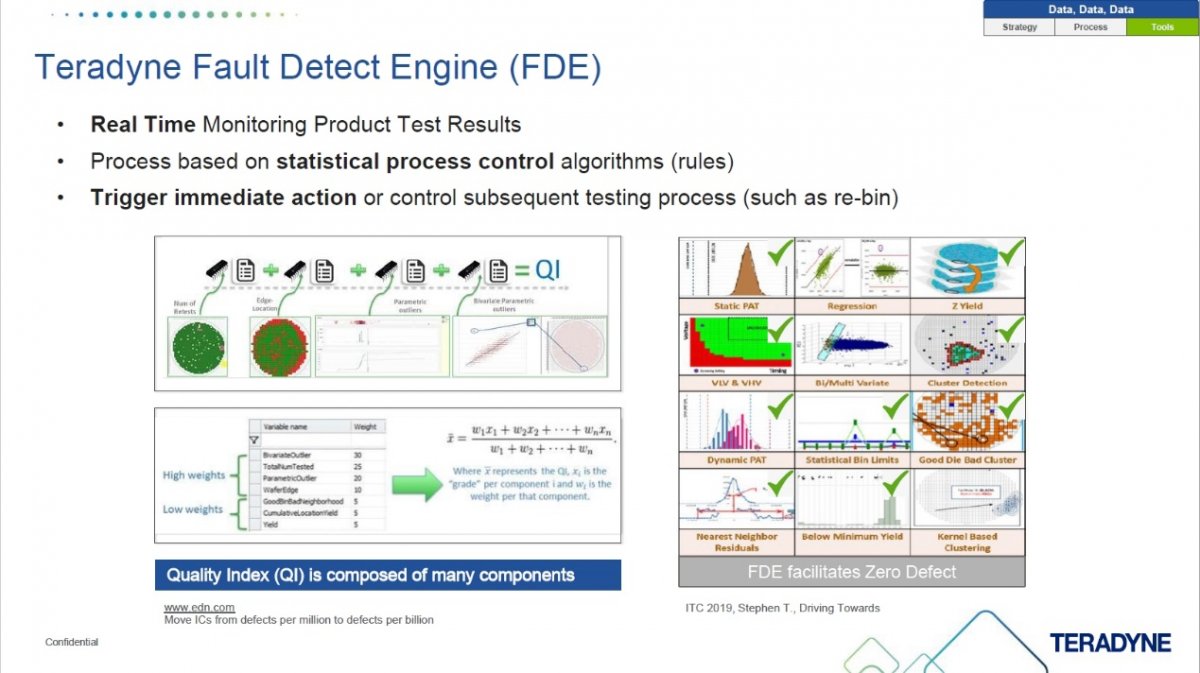

值得注意的是,UltraEDGE Server、FD Engine、Oasis辅助工具都使用了AI技术。黄飞鸿说,泰瑞达在3年前成立的一个研发团队,针对AI如何加速测试结果分析进行研究。“我们根据常见的芯片失效问题形成一个模板,以后可以预测该问题是否会提前出现。对测试来说是要产生不同的模板,且具备提前学习的能力,提前把一些故障或缺陷识别出来。”3svesmc

3svesmc

3svesmc

由于UltraEDGE可安装大数据分析软件,在车规芯片测试中更多用的是Dynamic PAT(动态模板,DPAT)。以晶圆测试阶段为例,针对每个晶圆来动态改变测试的灵敏度就叫动态分析。不过,数据的分析最终是看质量指标,不是只看最早的测试结果。涉及到车身安全、行车安全的标准很严格,在晶圆测试阶段测一遍,封装好后在老化前、老化后测三遍,芯片测试端至少有9道工序。因此,数据分析软件对实现0 DPPM目标极其重要。3svesmc

最后,黄飞鸿也补充表示,其实车规芯片与非车规芯片,使用类似的测试设备,不同的是后面的数据处理,比如UltraEDGE、FD Engine的统计分析,车规芯片测试的要求更高,它不只是单纯测试性能规格,而是要看它的统计分布,在每个晶圆上的物理分布、最低良率要求、不同温度下的表现。通过统计分析排布后,再去综合判断是否合格,其背后的支撑是大数据分析。3svesmc

-

微信扫一扫,一键转发

-

关注“国际电子商情” 微信公众号

- 上市分销商2024年度业绩快报抢先看

2024年,6家上市分销商中有3家实现归母净利润同比增长。

- Q1财测大降25%,安森美称将“精简”业务

在全球半导体行业面临增长放缓的背景下,安森美(onsemi)在2024年第四季度业绩下滑,并预计2025年第一季度营收将大幅下降。为应对市场挑战,公司宣布将采取“精简”业务等措施以提升竞争力……

- 计划融资超40亿,哪吒汽车等待“复活”

工厂正待复产……

- 巴黎AI峰会现分歧:联合声明遇冷,“空谈”质疑待解

当地时间2月10 - 11日,由法国、印度联合主办的人工智能行动峰会(AI Action Summit)在巴黎大皇宫隆重举行。

- 汽车巨头紧急呼吁重启美国50亿美元充电计划:仅建126个

美国50亿美元的电动汽车充电计划陷入停滞,仅建成126个充电桩。汽车巨头们终于坐不住了,紧急呼吁政府重启这一关键项目……

- 2024年全球手机销量前十榜单公布,谁是全球销量冠军?

近日市场研究机构Counterpoint Research和Canalys均发布了2024年全球销量前十的手机榜单。虽然其中有部分机型或者排名不同,但这两份榜单均仅有苹果和三星两大品牌入选……

- 半导体市场增长强劲,2024年销售额首破6000亿美元大关

国际电子商情10日讯 最新数据显示,2024年全球半导体行业迎来了历史性突破,销售额首次突破6000亿美元大关,达到6276亿美元,同比增长19.1%……

- 长安、东风汽车同日宣布重组,市场猜测可能合并

2月9日晚,中国兵器装备集团有限公司(简称“兵器装备集团”)旗下长安汽车、长城军工、建设工业等上市公司发布通告,透露接到兵器装备集团的通知,集团正在与其他国资央企筹划重组事宜。同日,东风汽车集团有限公司(简称“东风公司”)旗下的东风股份、东风科技也宣布,东风公司正在探讨与其他国资央企的重组可能性。

- 豪掷180亿韩元,韩国计划投资MicroLED

国际电子商情8日讯 韩国正加速布局下一代显示技术,计划投资180亿韩元推动MicroLED等技术研发,以巩固其全球市场地位。

- 韩国芯片巨头Magnachip寻求再次出售,LX集团或成最大赢

国际电子商情8日讯 在显示器行业长期低迷的背景下,曾因美国干预而搁置出售计划的韩国芯片制造商Magnachip,在时隔数年后再度寻求出售……

- 软银65亿美元收购Ampere谈判进入尾声,最快本月官宣

国际电子商情8日讯 软银集团(SoftBank)以65亿美元(含债务)估值对美国芯片设计公司Ampere Computing LLC的收购交易接近达成,最快可能在本月官宣。交易若最终完成,将成为2025年全球半导体行业最具标志性的并购事件之一……

- 2024年全球半导体市场增长18.1%,AI和数据中心成核心驱

国际电子商情7日讯 据市调机构Gartner近日发布的最新数据,2024年全球半导体市场收入总额达6260亿美元,同比增长18.1%,

- 全球半导体设备市场,方兴未艾!

近日,Tokyo Electron(以下简称“TEL”)宣布,将在日本宫城县建造一座新的生产大楼,由TEL的制造子公司TEL宫城公司

- 中国北大研究团队,氮化镓技术获新进展

近日,北京大学物理学院杨学林、沈波团队,联合宽禁带半导体研究中心等多个科研机构,在氮化镓外延薄膜中位错的原

- 2025年数据中心五大趋势

数据中心/云计算可以说是人工智能领域的核心,占据了英伟达总收入的85%~90%。

- 重庆发布新政,聚焦高端芯片与器件发展

近日,重庆市人民政府办公厅印发《重庆市推动经济持续向上向好若干政策举措》,提出支持科技领军企业、产业链龙

- 消息称苹果取消Mac连接AR眼镜,独立AR眼镜研发仍推进中

2月10日消息,据彭博社记者马克·古尔曼报道,苹果公司取消了一款与Mac连接使用的AR眼镜项目,但仍在积极推进独立

- 三星2nmSF2工艺试产良率约30%?

韩国媒体TheBell报道,三星正在为旗下自研处理器Exynos2600投入大量资源,以确保其按时量产。

- 2024年Q4平板电脑市场整体增长放缓,iPad占据40%市场份额

尽管全球平板电脑市场在2024年的大部分时间都保持着两位数的增长,但在2024年Q4,平板电脑出货量仅同比增长3%。

- AR微显示厂商Cellid完成1300万美元融资

2月7日,日本AR眼镜光学厂商Cellid宣布,公司通过定向增发完成总额1300万美元(约人民币9478.95万元)的融资。

- 多家半导体大厂官宣换帅!

近日,多家媒体发布消息称,瑞芯微前副总经理陈锋将出任Arm在中国的合资公司安谋科技首席执行官(CEO)一职。

- 全球半导体厂商营收10强排行榜出炉!

美国市场研究机构Gartner发布2024年全球半导体厂商营收排行榜。

- 2024年先进封装晶圆占比近半

随着传统扩展方式的成本和复杂性上升,先进封装已成为满足人工智能(尤其是大型语言模型训练)性能需求的一种方式

- 2024年AIPC未能提振笔电市场,仅从2023年的低点温和增长5%

2024年Q4,全球笔记本电脑出货量同比增长了6%,达到5450万台。

- 英飞凌在泰国新建后道工厂,优化和丰富生产布局

英飞凌位于曼谷南部沙没巴干府的新后道厂破土动工,该厂将扩大公司在亚洲的生产布局。

- 芯耀辉:从传统IP到IP2.0,AI时代国产IP机遇与挑战齐飞

2024年,集成电路行业在变革与机遇中持续发展。面对全球经济的新常态、技术创新的加速以及市场需求的不断变化

- 艾睿电子与印尼初创协会合作,支持本地科技初创公司

雅加达,印尼- 2025年1月14日 - 全球技术解决方案供应商艾睿电子(Arrow Electronics)与印尼初创协会合作(STARFIN

- 【凯新达科技】新年欢聚,共绘年会精彩篇章!

无畏挑战 共创未来祥龙回首留胜景,金蛇起舞贺新程。在2025年元旦新年之际,深圳市凯新达科技有限公司(以下简

- CES 2025新品:摩尔斯微电子推出Wi-Fi芯片MM8108

最新Wi-Fi HaLow片上系统(SoC)为物联网的性能、效率、安全性与多功能性设立新标准;

配套USB网关,轻松实现Wi- - ST与彭水共绘可持续发展新篇章

随着与三安光电的碳化硅合资工厂落地重庆,2024年6月,意法半导体与重庆市彭水自治县同步启动了可持续发展合作

- 【凯新达科技】2025年度旅游活动景点精彩报道

凯新达科技 自由之旅 征途同行

- 超高性价比AI电脑:英伟达NVIDIA Jetson Orin Nano Super真香!iCEas

NVIDIA Jetson Orin™ Nano Super 开发者套件是一款尺寸小巧且性能强大的超级计算机,重新定义了小型边

- TI推出新一代支持边缘AI的雷达传感器和汽车音频处理器,改进车内驾

德州仪器今日推出了全新的集成式汽车芯片,能够帮助各个价位车辆的驾乘人员,实现更安全、更具沉浸感的驾驶体验

- 【原厂入驻】飞虹半导体现已入驻iCEasy商城!

广州飞虹半导体科技有限公司成立于广州越秀区,诚信经营20多年。主要研发、生产、经营:场效应管、三极管等半

- 携手共进,江波龙与电子五所在中山展开深度交流

近日,半导体存储品牌企业江波龙与工业和信息化部电子第五研究所(中国赛宝实验室,以下简称“电子五所”)在江波龙

- 【原厂入驻】迈巨微电子现已入驻iCEasy商城!

深圳迈巨微电子有限公司深耕锂电池管理芯片领域,围绕电池健康和安全,电池电量计算二个核心技术能力,提供完善的