究竟谁握有最佳的半导体工艺技术?业界分析师们的看法莫衷一是。但有鉴于主题本身的复杂度以及芯片制造商传递的信息不明确,就不难了解为什么分析师的看法如此分歧了。uzLesmc

市场研究机构Linley Group首席分析师Linley Gwennap表示,英特尔(Intel)将在10nm工艺优于台积电(TSMC)与三星(Samsung),就像在14nm时一样。VLSI Research执行官G. Dan Hutcheson认为,台积电即将量产的10nm工艺将大幅超越英特尔的14nm节点,而且台积电正以较英特尔更快的速度超前进展。此外,International Business Strategies (IBS)创办人兼执行长Handel Jones则指出,英特尔与台积电的10nm工艺技术性能旗鼓相当。uzLesmc

但各方均同意,有多种变量决定了组件如何制造,对于不同类型芯片的影响也各不相同。分析师们还把责任归咎于营销部门,认为他们经常是让情况变得更加模糊,而非厘清现实。uzLesmc

“事实上,没有一种衡量方式能够决定一项技术的性能、功耗与晶体管密度,”Jones说,“金属层M1间距十分重要,但局部互连也会影响到布线的闸极密度与性能;闸极间距对于闸极密度相当重要,但鳍片高度也明显影响性能。”uzLesmc

“互连延迟正成为重大的挑战,尤其是在10nm时有80%的性能都取决于互连延迟的影响,”他补充说。

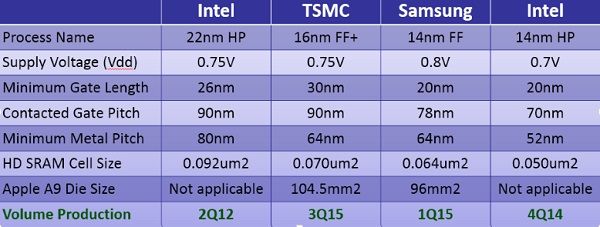

从Linley Group的衡量指标来看,英特尔比台积电和三星更具优势(来源:Linley Group)uzLesmc

从Linley Group的衡量指标来看,英特尔比台积电和三星更具优势(来源:Linley Group)uzLesmc

FinFET的高度与线宽可作为衡量技术节点与芯片制造商实力的良好指针。Hutcheson认同这一观点,他并表示,SRAM的单元尺寸也值得考虑。uzLesmc

但是,“我认为技术进展的终极衡量标准在于随着每一技术节点倍增密度的能力,”Hutcheson说,“英特尔至今在每一节点都达到了这一目标。”uzLesmc

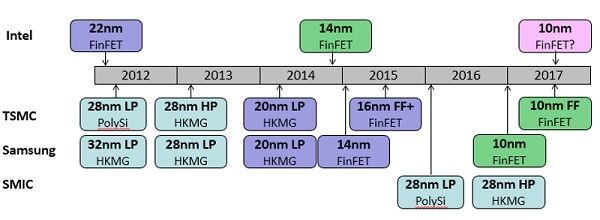

也就是说,台积电在10nm达到的M1金属层间距已能“完整微缩(~70%),领先英特尔的14nm,”Hutcheson强调,英特尔持续14nm节点也已经2年了。uzLesmc

随着近期披露10nm与7nm计划,“台积电不仅证明拥有扳回胜局的魔力,同时还踩着比任何人更快的进展步调,”他补充说。uzLesmc

同时,尽管在今年1月,一些厂商还不那么看好其16/14nm节点,但台积电目前的16nm节点“在相同的时间架构下,已经在营收与良率方面双双超越了28nm,”他强调。uzLesmc

节点性能与名称无关?

Gwennap表示,技术节点的传统衡量标准是晶体管尺寸,亦即所测得的最小闸极长度。然而,归功于市场营销的努力,如今的节点名称不再与闸极测量结果吻合了,“但其差距也不算太大——英特尔14nm工艺的闸极长度约相当于三星(Samsung)的20nm。”uzLesmc

不过,Gwennap说,台积电和三星目前“在速度与密度方面都远落后英特尔的14nm工艺,”以此来看,他认为三星的节点更适合称为17nm,台积电则为19nm。“预计在10nm时的情况类似...三星与台积电将在速度与密度方面落后英特尔约一至半个节点。”uzLesmc

然而,光是最小闸极长度并不足以决定一切,Chipworks资深研究员兼技术分析师Andy Wei表示,“定调一项技术是否最优,高度取决于与面积微缩有关的工艺成本。而这可归结为比较布线单元级的技术能力,以及达到该密度所需的成本,Chipworks正是以此作为基准。”

Linley Group认为,三星可望最先推出10nm工艺,但英特尔的表现会更优(来源:Linley Group)uzLesmc

Linley Group认为,三星可望最先推出10nm工艺,但英特尔的表现会更优(来源:Linley Group)uzLesmc

自从德州仪器(TI)为了如何衡量闸极长度而战,工艺节点的命名之争已经持续25年了。Hutcheson说,TI采用有效闸极长度,而硅谷芯片制造商则以更大的闸极长度作为指标。uzLesmc

在1990年代,当线宽微缩至纳米级时,“新的论据认为闸极长度不再适用,因为蚀刻削薄而使M1金属级间距成为更适合的标准——不过却仍由闸极长度决定性能。”uzLesmc

其后,台积电宣称其40nm工艺比英特尔使用的45nm节点更好,但除了“更好”似乎也没提出任何指标,Hutcheson指出,“从那时起,就一直有点像 是『各自表述』一样。例如,Globalfoundries的32nm和28nm之间真正的差异是32nm是SOI工艺,28nm则是bulk工艺。”uzLesmc

台积电已经明确表示其16nm工艺采用20nm的后段工艺技术——FinFET晶体管层迭于顶部。在最近于圣荷西举行的会议,台积电表示,其7nm节点将会较其10nm工艺密度更高1.63倍,Chipworks的Wei说,“这使得2种尺寸微缩0.7倍的性能提高还不到2倍,而节点名称微缩了0.7倍。”uzLesmc

“市场营销元素强烈影响节点的命名,而且着眼于顶级规格,但设计工程师知道他们所选择的技术优点,”Jones表示。毕竟,“只要工艺技术快速、低功耗且低成本,那么怎么称呼都不重要。”uzLesmc