例如在体育赛事和电脑游戏活动直播不断风靡的推动下,4K视频和H.265编码算法迎来大发展,传统CPU开始难以应对所需的帧速率。与此类似,人工智能也正通过将海量数据用于培训神经网络,供其学习和识别数据中的模式,再被用于图像识别、自动驾驶、搜索优化和自然语言翻译等多种不同应用。在这两大领域中,数据中心越来越多地使用专用加速器来实现对用户查询的低延迟响应。aIYesmc

Intel: 我们支持ARM内核

英特尔(Intel)公司全球副总裁兼中国区总裁杨旭在2016年11月举办的英特尔SoC FPGA开发人员论坛(ISDF)上,再一次向业界做出包括投资新的FPGA和SoC FPGA产品路线图、支持更长的产品生命周期、继续为客户提供一流的服务与支持、以及继续支持Altera SoC FPGA中ARM内核在内的四大承诺。aIYesmc

他表示,当今技术正在不断“打破数字世界与真实世界之间的藩篱”,Intel内部将物、设备与云之间的关系称为“增长的良性循环”,一系列的技术通过这个循环增强了它们的价值,也促使英特尔不断调整自身战略。而FPGA的独特性与灵活性在智能化连接领域中扮演着极具差异化优势的角色,这也是为什么Intel愿意斥资167亿美元收购 Altera的根本原因。aIYesmc

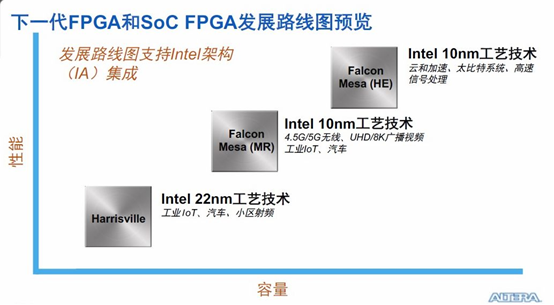

根据规划,英特尔下一代FPGA和SoC FPGA产品的发展路线图将分为低中高三个产品平台(图1),并支持Intel架构(IA)集成。其中低端产品主要应用于工业IoT、汽车和小区射频领域,采用英特尔22nm工艺技术;中端产品主要应用于4.5G/5G无线、UHD/8K广播视频、工业IoT和汽车领域,采用英特尔10nm工艺技术;高端产品主要应用于云和加速、太比特系统、高速信号处理领域,采用英特尔10nm工艺技术。

图1:英特尔下一代FPGA和SoC FPGA发展路线图aIYesmc

英特尔承诺会根据不同的客户需求提供不同的异构架构,包括:分立的CPU+FPGA、封装集成的CPU+FPGA、以及将Intel CPU/FPGA/ARM三者进行管芯集成的FPGA。aIYesmc

作为目前英特尔性能最为强劲的FPGA产品,Stratix 10 FPGA/SoC FPGA系列的所有型号都采用异构3D SiP集成技术,通过使用Intel专用嵌入式多管芯互联桥接(EMIB)技术将高密度单片FPGA内核逻辑、高速串行收发器和协议块集成在一起。此外,该系列也是第一款采用HyperFlex新体系结构的器件。通过在所有内核互联布线段上引入寄存器,Stratix 10系列能够有效减少布线延时,提升整体性能。aIYesmc

Xilinx:可重配置加速堆栈提升2-6倍计算效率

作为FPGA技术的发明者,赛灵思(Xilinx)公司过去几年在数据中心应用中取得了巨大发展。赛灵思战略与市场营销部高级副总裁Steve Glaser提供的相关资料显示,目前全球七大超大规模云服务公司中已有3家采用了赛灵思FPGA,其中百度已于2016年10月宣布设计出赛灵思UltraScale FPGA池,以加速机器学习推断;2016年5月,赛灵思携手AMD、ARM、华为、IBM、Mellanox和高通共同成立智能高速缓存一致性互联标准(CCIX)联盟,5个月后成员数量已激增为成立之初的3倍;11月,赛灵思发布采用高带宽存储器(HBM)和CCIX技术的最新16nm Virtex UltraScale+ FPGA产品,在将存储器带宽提升20倍的同时,还将单位比特功耗降低4倍。

赛灵思云计算战略市场开发总监Andy WalshaIYesmc

然而,FPGA一直存在编程难的问题,而且需要相关人员同时具备软硬件技能。为了更好地满足新兴市场需求,继2014年发布针对FPGA加速的SDAccel软件定义开发环境后,赛灵思于2016年底针对超大规模数据中心领域发展最快的三大计算密集型应用:机器学习、数据分析和流媒体视频直播,推出可重配置加速堆栈。aIYesmc

这意味着赛灵思提供的将不止是FPGA芯片,还包括优化的数学函数库与应用函数库(如用于机器学习的Caffe)、软件框架实现方案、支持OpenCL和C/C++等高级语言的工具、便于配置和管理的 Openstack支持,以及预期的加速器板参考设计。赛灵思云计算战略市场开发总监Andy Walsh称,通过赛灵思FPGA,该可重配置加速堆栈方案提供了比x86服务器CPU高40倍,比竞争型FPGA方案高6倍的业界最高计算效率。通过切换至最佳设计比特流,对这些工作负载的优化仅需毫秒级即可完成。aIYesmc

“一个加速器在某项特定工作负载下可能很快,但还必须要看它能否能降低数据中心的整体运营成本。”Andy Walsh解释说,加速技术的总拥有成本有两大决定性因素:加速器可支持的应用广度,以及加速器如何能够针对这些应用方便高效地配置和池化,从而确定加速器的利用率。 aIYesmc

赛灵思战略与市场营销部高级副总裁Steve GlaseraIYesmc

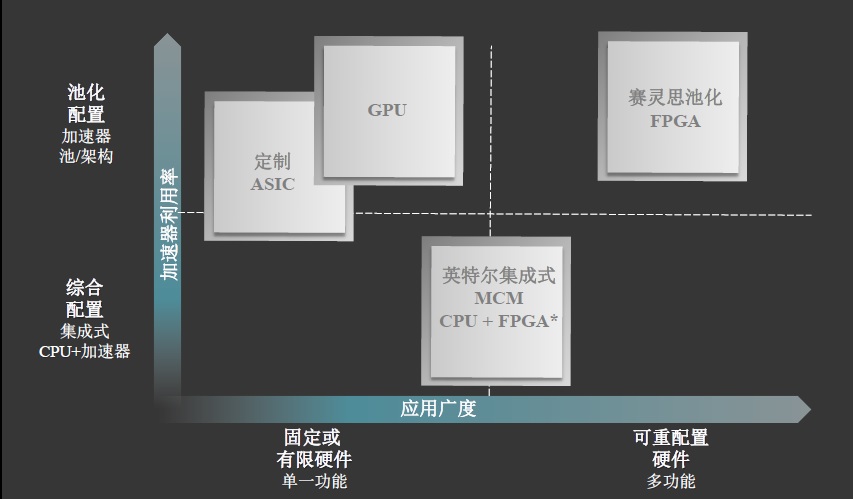

图2列出了用于加速数据中心工作负载的不同可选方案:CPU、定制ASIC、GPU和 FPGA。在Andy Walsh看来,GPU和定制ASIC虽然也采用池化配置部署以提高利用率,但二者都不能支持广泛的应用。由于缺乏可重配置性,二者也只能支持与其固定硬件架构相匹配的工作负载。此外,创建定制ASIC所带来的巨大的设计投入、设计风险和和设计成本,使其相比FPGA十分不划算,缺乏经济性。aIYesmc

至于Intel提出的集成式CPU-FPGA设计的战略,他认为该方案限制了应用的广度和加速器的利用率,使其进入了“无人区(no man’s land)”。这种CPU+FPGA的器件受功耗密度的限制,通常限制FPGA只能是中低端器件和有限的工作负载。FPGA集成在CPU套件中,也会限制池化加速器的能力,从而大幅降低其利用率。

图2:用于加速数据中心工作负载的不同方案在应用广度与利用率上的区别(来源:赛灵思)aIYesmc

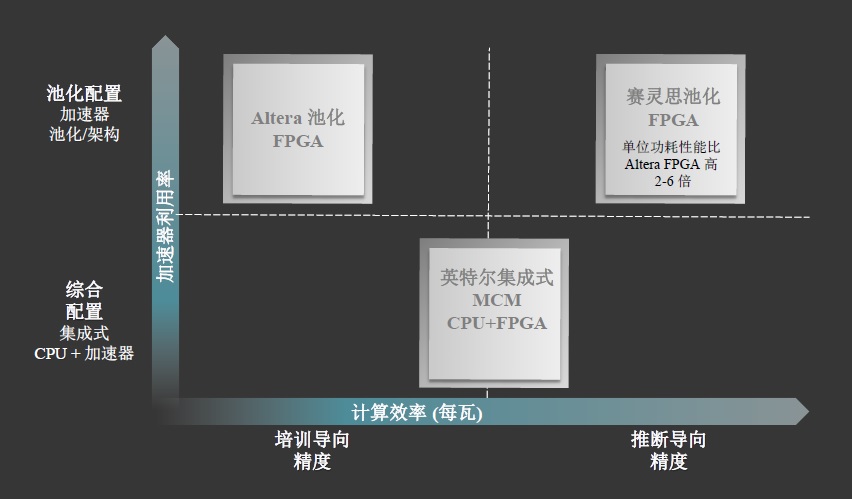

“Altera强调浮点精度DSP,这与包括机器学习推断在内的众多应用并不匹配,而且远低于针对训练优化的GPU的计算效率。”Andy Walsh说,就计算效率而言,赛灵思FPGA比Altera独立FPGA高出2-6倍,相比Intel集成式MCM利用率则大幅提升,其优势源于出色的DSP架构、存储器层级结构和芯片技术的领先地位。aIYesmc

图3:用于加速数据中心工作负载的不同方案在利用率与计算效率上的区别(来源:赛灵思) aIYesmc

《国际电子商情》原创文章,转载请注明原文地址和链接aIYesmc

aIYesmc aIYesmc

aIYesmc