7nm晶片来了!三星量产7LPP EUV制程

2018-10-19 09:53:16

继台积电(TSMC)于本月初投片采用EUV微影技术的首款7+奈米晶片后,三星电子(Samsung)也宣佈投片并逐步量产多款7奈米(nm) EUV晶片。为了迎头赶上台积电的生态系统,三星还将大力支持其IP和EDA基础设施,并详细介绍其封装能力。

晶圆代工大厂——台积电和三星争相较劲先进制程,究竟谁能最先推出首款采用极紫外光(EUV)微影技术制造的7奈米晶片?tS3esmc

继台积电(TSMC)于本月初投片采用EUV微影技术的首款7+奈米晶片后,三星电子(Samsung)也宣佈投片并逐步量产多款7奈米(nm) EUV晶片。为了迎头赶上台积电的生态系统,三星还将大力支持其IP和EDA基础设施,并详细介绍其封装能力。tS3esmc

在本週于美国硅谷举行的Samsung Tech Day上,三星宣佈采用EUV的7奈米LPP (Low Power Plus)制程研发完成,正式进入商用化量产,未来也将在此技术基础上朝5nm、3nm前进。此外,三星并宣佈出样基于其16-Gbit DRAM晶片的256-GByte RDIMM,并计划采用内建赛灵思(Xilinx) FPGA的固态硬碟(SSD)。tS3esmc

不过,7nm商用化量产还是此次活动的亮点,再加上该公司内部开发的EUV光罩检测系统,正象徵著三星的一个发展里程碑。tS3esmc

相较于其10nm节点,三星的7LPP制程能缩小多达40%的晶片面积,速度提高20%,并降低50%的功耗。此外,三星表示目前拥有50家代工合作伙伴,包括Ansys、Arm、Cadence (拥有7nm数位和类比设计流程)、Mentor、Synopsys和VeriSilicon,均表示采用7nm制程投片。tS3esmc

据称7LPP制程吸引了多方的兴趣,包括网路巨擘、网路公司和高通(Qualcomm)等手机供应商等客户。然而,三星预计最早要到明年年初之后,才可能会有客户发佈相关消息tS3esmc

三星代工行销总监Bob Stear表示,自今年初华城S3厂引进EUV设备以来,EUV系统一直维持在支援250W光源。目前的功率级可将产量提高到生产1,500片晶圆/天。他说,从那以后,EUV系统逐渐可达到280W峰值,而三星的目标是进一步提高功率到300WtS3esmc

tS3esmc

tS3esmc

三星华城S3厂EUV产线(来源:Samsung)tS3esmc

Stear指出,相较于传统氟化氩(ArF)系统需要五层光罩,EUV所需的层数较少,因此降低了成本而使得良率提升。不过,该技术节点在前段制程(FEOL)仍然需要进行多重曝光。tS3esmc

三星开发了自家的系统,用于比较并调整预期和实际的光罩图案,以加速其EUV投产。由于目前尚不清楚它是否与典型的第三方检测系统一样自动化,VLSI Research执行长G. Dan Hutcheson认为它更像是一套光罩检查系统。tS3esmc

三星预计其7nm节点将在今年年底前通过Grade 1 AEC-Q100汽车标准。在封装方面,三星正在开发一种重分佈层(RDL)中介层,可在单个元件上安装多达8个高频宽记忆体(HBM)堆叠。该公司并致力于在基板中嵌入被动元件,以节省资料中心晶片的空间。tS3esmc

tS3esmc

tS3esmc

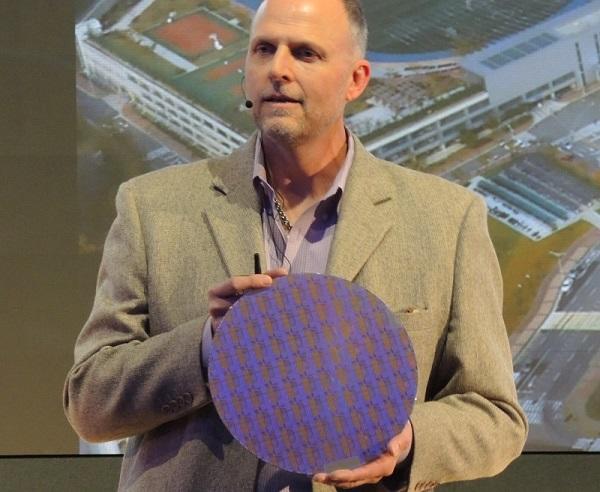

三星代工行销总监Bob Stear展示三星S3厂生产的7nm EUV晶圆(来源:EE Times)tS3esmc

市场研究机构International Business Strategies (IBS)执行长Handel Jones说,三星和台积电在7nm阶段都可能只将EUV用于两个晶片层,因为光罩护薄还在开发中,因此至今还未能使用。到了5nm时,他们很可能将EUV扩展至6层,但这至少要到2021年后了,届时的光罩护膜将有足够的耐用性和光传输能力。tS3esmc

Jones说:「三星大约提前了六个月采用EUV制程,因为他们一直在DRAM和逻辑制程中使用这一系统,但台积电在使用IP和工具方面处于领先地位,而且也有更多的客户合作关系,如超微(AMD)、苹果(Apple)、海思(HiSilicon)和辉达(Nvidia)等。」tS3esmc

另一位分析师表示,思科(Cisco)原本是IBM代工业务的客户,目前正与台积电合作开发7nm产品。而高通的7nm设计预计将分别交由台积电和三星代工。tS3esmc

尽管如此,Jones预测这家韩国巨擘的营收可望在今年达到900亿美元,甚至到2027年可能超过1,500亿美元。从三星记忆体业务的成长力道来看,Jones估计其DRAM和NAND销售将分别达到50%的和45%的佔有率。tS3esmc

三星可望顺利在明年6月之前开始量产5nm和4nm节点,在相同的技术基础上实现突破性的进展。Stear说,这一制程节点的PDK预计在今年年底前发佈,并将在S3厂旁为EUV打造另一条产线。tS3esmc

这三种制程节点将使触点更接近并最终移动到闸极上方,以增加密度并减少金属间距。这是英特尔(Intel)先前针对其10nm节点所讨论的一种方法,但尚未量产。tS3esmc

Stear说:「我们正逐步处理闸极上触点(contact-over-gate)。正如有些人发现的,这是一个难以解决的问题。」tS3esmc

三星于今年5月宣佈计划转向闸极全环(gate-all-around;GAA)电晶体,或称为奈米片,用于3nm节点。其目标在于将标称电压降至新低点,以持续降低功率。预计在今年六月就能提供用于3nm节点的第一版0.1 PDK。tS3esmc

tS3esmc

tS3esmc

三星介绍内部开发的一系列封装技术进展tS3esmc

在其核心记忆体业务方面,三星表示开始出样采用其16-Gbit晶片制造的256GB RDIMM。这些储存卡能以高达3,200MHz的DDR4速度运行,支援50ns读写,应该可以在今年年底前投产。tS3esmc

这些记忆体晶片采用一年前发佈的1y奈米制程制造。但未来1y制程是否导入EUV,目前尚不清楚。然而,三星DRAM开发主管Seong Jin Jang指出,后续的1z和1a制程节点将越来越广泛地使用EUV。tS3esmc

三星并展示在AMD EPYC伺服器上运行的八个DIMM。相较于其现有的128GB卡在225W时提供380万次运算/秒,这些DIMM则能在170W时达到每秒320万次运算。tS3esmc

最终,三星的目标是将DIMM提高到768GBytes,最终在于使HBM资料速率从目前的307GB/s提高到512GB/s。他并补充说,GDDR6绘图记忆体将从目前的18Gbits/s提高到22Gbits/s,而LPDDR记忆体功耗则将从24mW/GB降至12mW/GB,但他并透露何时实现。tS3esmc

此外,三星宣佈计划采用嵌入式Xilinx Zynq FPGA的智慧SSD,将性能提升2.8倍至3.3倍。这些装置适用于各种资料库、AI、视讯和储存等应用。tS3esmc

该公司表示,该SSD将提供一种更易于扩展性能的方法,而不必再采用标准FPGA搭配独立加速器的作法。目前仍在原型阶段的这些SSD产品将采用各种密度和中阶FPGA。tS3esmc

tS3esmc

tS3esmc

三星所谓的智慧SSD目前都还只是原型,并未透露任何规格或何时推出tS3esmc

编译:Susan HongtS3esmc

(参考原文:Samsung Ramps 7nm EUV Chips,by Rick Merritt)tS3esmc

微信扫一扫,一键转发

关注“国际电子商情” 微信公众号

美通社消息,3月14日,“2025英飞凌消费、计算与通讯创新大会”(ICIC2025)在深圳举行。本届大会汇聚600多位业界精

近日,湖南省工信厅发布了《2025年湖南电子信息制造业重点项目名单》,涵盖先进计算、音视频、新一代半导体、人

3月15日,质鼎集团公众号消息,惠科东莞平板显示集群电子商务项目二期正式开工。

富士康、台积电、广达、华硕、联发科、友达光电等中国台湾20家电子企业2024年第四季度和全年财报汇总。

近年来,LED显示屏市场持续演进。回顾2024年,行业呈现出哪些发展态势?展望2025年及未来,市场又将面临哪些机遇与

近日,索尼正式发布新一代RGBLED背光技术系统,可实现4000尼特峰值亮度。索尼计划该系统将于2025年开始量产,并将

AI芯片是半导体最大的增长点,先进封装则是制造AI芯片的关键技术。此前英伟达H100成本约3000美元,而用先进封装

截止2024年底,17家欧美固态电池企业融资总额已突破42亿美元。

曾几何时,中国半导体几乎不断有大基金投资、大项目上马,以及美国制裁的新闻。长期处于聚光灯下,中国半导体成为

Dynabook在退出十年后宣布重返美国消费市场。

Canalys最新数据显示,受到消费需求激增8%的推动,2024年第四季度中国大陆的PC市场开始复苏,同比增长2%。

根据TrendForce集邦咨询最新调查,2024年第四季由于Apple(苹果)手机生产进入高峰,以及中国部分地方提供消费补贴

德州仪器近日推出了全球超小型 MCU,进一步扩展了品类齐全的 Arm® Cortex®-M0+ MSPM0 MCU 产品组合。

创新是企业持续发展最大的价值。

“闪迪(Sandisk)又回来了!”在3月12日的存储年度盛会CFMS MemoryS 2025上,闪迪公司全球产品副总裁Eric Spa

摩尔斯微电子推出合规的Wi-Fi HaLow片上系统(Soc),开启欧洲连接技术新纪元。超低功耗、远距离连接功能现已为

CFMS | MemoryS 2025已圆满落幕,期间包括三星电子、长江存储、铠侠、美光、闪迪、高通、Arm、慧荣科技、S

Hyperlux™ ID iToF 系列将深度测量距离提升至最远 30 米,提高工业环境中的生产效率和安全性

26TB大容量CMR HDD助力WD Red Pro与G-DRIVE/G-RAID系列专业级产品矩阵,赋能数据存储拓展与生产力跃升

全新一代MCU可以满足各种区域控制架构和电气化系统需求,助力汽车制造商向软件定义汽车(SDV)过渡。

将出色的高

聚洵半导体科技(上海)有限公司(Gainsil Semiconductor Technology)于2016年成立于上海张江科学城,是一家全球

领域新成果领域新成果4月必逛电子展!AI、人形机器人、低空飞行、汽车、新能源、半导体六大热门新赛道,来NEPCO

后量子加密技术帮助保护数字基础设施免受量子计算机在将来带来的潜在威胁。

英飞凌坚信低碳化和数字化是未来十年的关键驱动力,半导体在应对能源挑战和推动数字化转型中扮演着重要角色。

点击查看更多

北京科能广告有限公司深圳分公司 版权所有

分享到微信

分享到微博

分享到QQ空间

推荐使用浏览器内置分享

分享至朋友圈