UltraFLEXplus: 为芯片质量最后一道防线提供保障

2022-01-15 13:19:10

芯片测试是半导体研发到量产全部流程的最后一道防线,包括晶圆测试和成品测试。通过测试,厂商能够及时发现芯片设计制造问题,进而提高芯片生产良率,保证出货质量

5G、AI、物联网等技术的进一步深化落地,推动了芯片制造向更高集成度、更高性能以及更小尺寸的方向发展。芯片集成的功能越来越多,工艺尺寸却越来越小,这也势必致使测试数据量呈指数级增长、芯片缺陷率有所上升。为满足日趋复杂的测试需求,芯片测试技术也在迅速迭代、不断演进。G2Qesmc

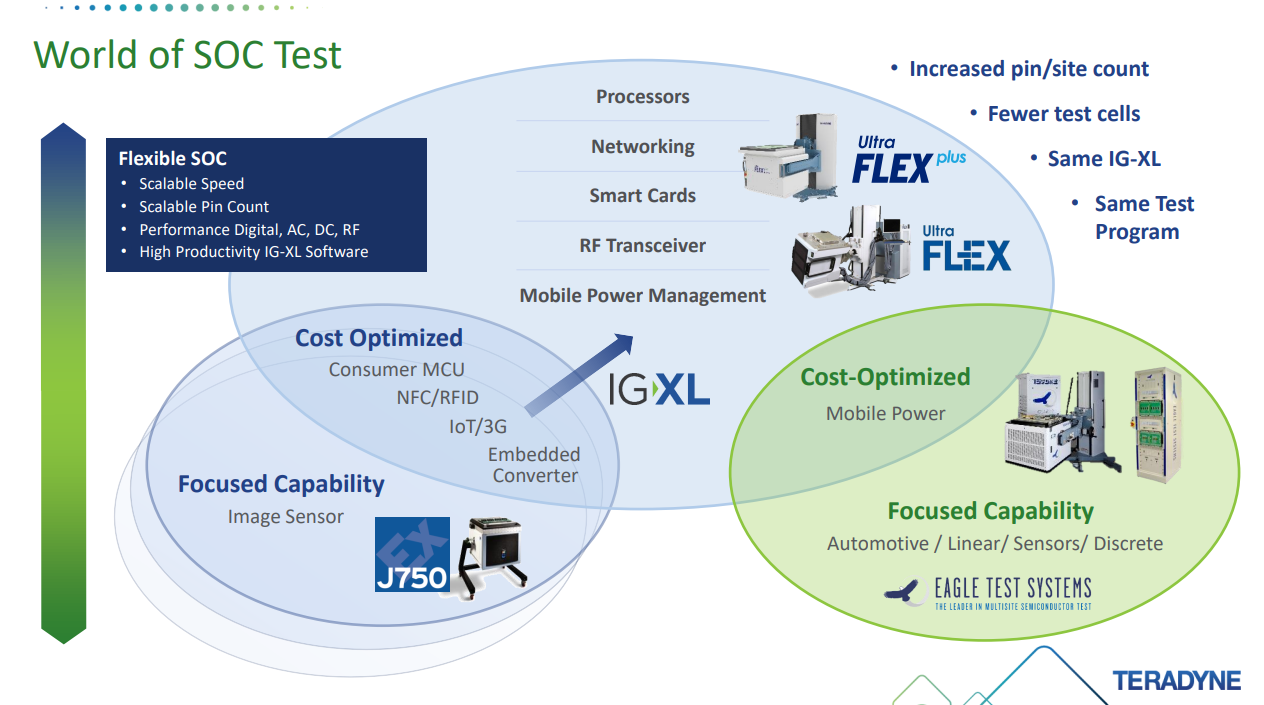

在半导体测试设备市场中,ATE测试设备占据了半导体测试设备的三分之二。其中,泰瑞达作为全球半导体测试技术、设备和市场占有率的姣姣者,拥有完整的半导体测试解决方案。G2Qesmc

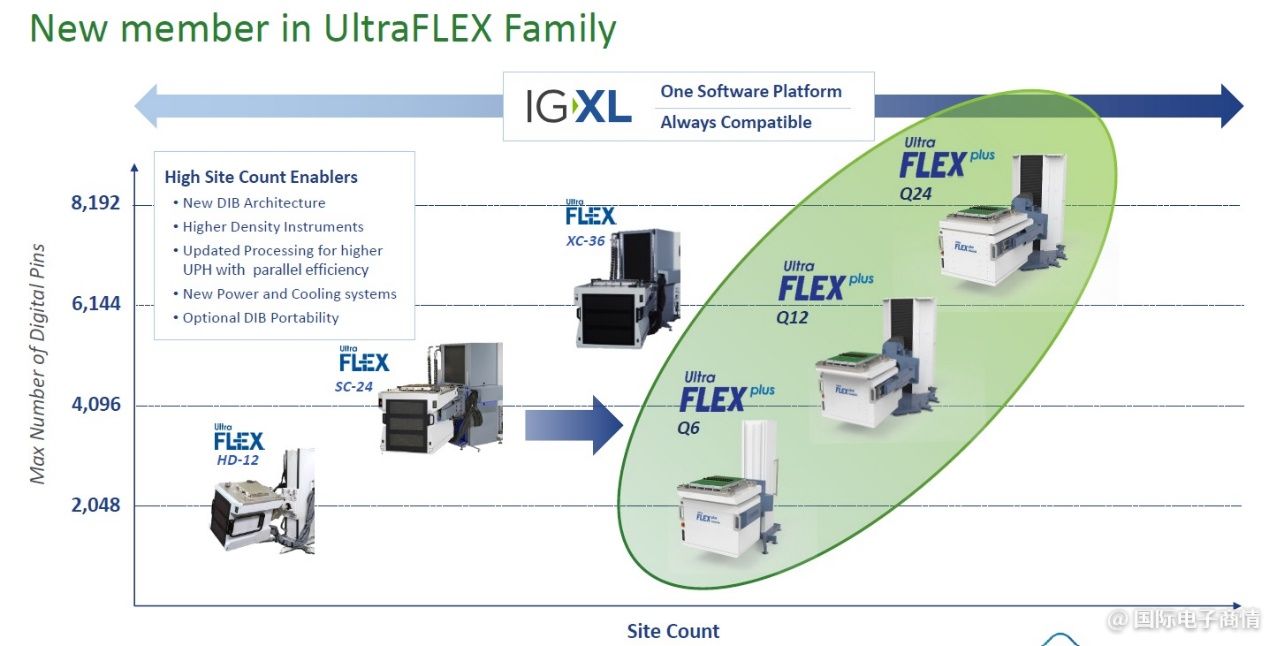

UltraFLEXplus是泰瑞达最新推出的高性能SoC测试平台,特点是在提高性能的同时大幅提升芯片测试工位的数量,并兼容IG-XL测试软件平台。目前,UltraFLEXPlus提供Q6、Q12到Q24不同机台的配置。G2Qesmc

G2Qesmc

G2Qesmc

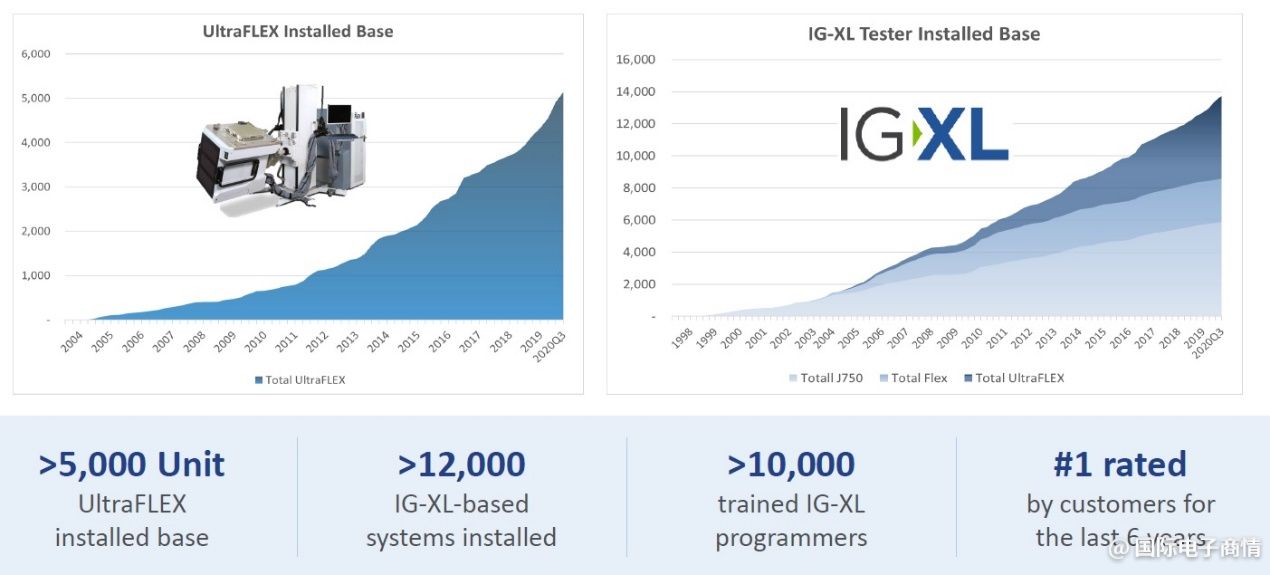

作为泰瑞达UltraFLEX家族的新成员,UltraFLEXplus是专为AI和5G网络部署中必不可少的处理器和ASIC芯片提供的测试方案,能与全球已安装使用的5000多套UltraFLEX系统无缝兼容,并使用IG-XL测试软件平台。该软件装机量超过1.2万套,并连续6年被评为半导体测试行业使用量第一的软件。G2Qesmc

G2Qesmc

G2Qesmc

在TERADYNE媒体沟通会上,泰瑞达中国区销售副总经理黄飞鸿表示:“芯片更新换代越来越快,开发周期越来越短,例如汽车电子芯片需要在两年内完成开发到上市的工作,相关从业人员的工作压力显著增加。这也意味着工程师需要一个更先进的测试平台来满足日益复杂的测试需求。”G2Qesmc

独有的PACE架构、Broadside应用接口以及IG-XL测试平台,被黄飞鸿视作UltraFLEXplus系列具竞争力的三大要点。G2Qesmc

G2Qesmc

G2Qesmc

按照黄飞鸿的介绍,UltraFLEXplus引入了创新的PACE运行架构,可实现板卡控制下放,提升处理效率,还能以最小的工程量创造出最高的测试单元产能。其搭载的多核系统控制器能够保持板卡高效、协调工作,让制造商减少15%-50% 的测试单元部署。PACE架构还可以实现更高的工程生产力,从而助力工程师更快、更好地完成更繁重的测试任务。G2Qesmc

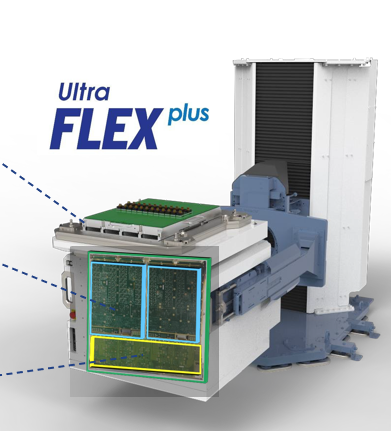

黄飞鸿表示:“我们对UltraFLEXplus平台的芯片测试接口板设计做了完全革命性的改进,采用Broadside技术可使接口板的应用区域扩大,减少接口板PCB层数,从而提高并行测试能力,降低测试难度。”与传统的 ATE 相比,Broadside DIB通过优化原本复杂的 DIB布局,使每个工位都能获得与之匹配的信号传输路径。这种颠覆传统的设计,使测试工程师能够更高效地对复杂芯片进行调试和特性分析,实现更高的测试机利用率,将新产品更快地推向市场。G2Qesmc

G2Qesmc

G2Qesmc

目前,泰瑞达旗下三种测试平台J750/UltraFLEX/UltraFLEXplus都已经得到了市场的检验与客户的认可。值得一提的是,三款产品均使用统一的测试软件平台:IG-XL,在测试程序方面可做到相互兼容,对测试工程师来说软件环境友好。“一个好的软件平台对于测试工程师来说非常重要。”黄飞鸿强调。G2Qesmc

G2Qesmc

G2Qesmc

泰瑞达中国区销售副总经理黄飞鸿G2Qesmc

关于疫情的对交货期的影响,“我们部分产品系列是在苏州伟创力生产。基于中国抗疫的出色表现,保证了全球90%以上的供货。我们现在交货周期大概是20周左右,不同的机台会有差异。作为对比,业界现在水准是40-52周。”黄飞鸿最后表示。G2Qesmc

芯片测试作为半导体产业链中不可或缺的一环,是决定一颗芯片能否被市场采用,并获得认可的基础。当前,如何提升芯片测试效率, 把控芯片测试质量,已经成为业界共同关注的焦点。G2Qesmc

微信扫一扫,一键转发

关注“国际电子商情” 微信公众号

近日,Tokyo Electron(以下简称“TEL”)宣布,将在日本宫城县建造一座新的生产大楼,由TEL的制造子公司TEL宫城公司

近日,北京大学物理学院杨学林、沈波团队,联合宽禁带半导体研究中心等多个科研机构,在氮化镓外延薄膜中位错的原

数据中心/云计算可以说是人工智能领域的核心,占据了英伟达总收入的85%~90%。

近日,重庆市人民政府办公厅印发《重庆市推动经济持续向上向好若干政策举措》,提出支持科技领军企业、产业链龙

2月10日消息,据彭博社记者马克·古尔曼报道,苹果公司取消了一款与Mac连接使用的AR眼镜项目,但仍在积极推进独立

韩国媒体TheBell报道,三星正在为旗下自研处理器Exynos2600投入大量资源,以确保其按时量产。

尽管全球平板电脑市场在2024年的大部分时间都保持着两位数的增长,但在2024年Q4,平板电脑出货量仅同比增长3%。

2月7日,日本AR眼镜光学厂商Cellid宣布,公司通过定向增发完成总额1300万美元(约人民币9478.95万元)的融资。

近日,多家媒体发布消息称,瑞芯微前副总经理陈锋将出任Arm在中国的合资公司安谋科技首席执行官(CEO)一职。

美国市场研究机构Gartner发布2024年全球半导体厂商营收排行榜。

随着传统扩展方式的成本和复杂性上升,先进封装已成为满足人工智能(尤其是大型语言模型训练)性能需求的一种方式

2024年Q4,全球笔记本电脑出货量同比增长了6%,达到5450万台。

英飞凌位于曼谷南部沙没巴干府的新后道厂破土动工,该厂将扩大公司在亚洲的生产布局。

2024年,集成电路行业在变革与机遇中持续发展。面对全球经济的新常态、技术创新的加速以及市场需求的不断变化

雅加达,印尼- 2025年1月14日 - 全球技术解决方案供应商艾睿电子(Arrow Electronics)与印尼初创协会合作(STARFIN

无畏挑战 共创未来祥龙回首留胜景,金蛇起舞贺新程。在2025年元旦新年之际,深圳市凯新达科技有限公司(以下简

最新Wi-Fi HaLow片上系统(SoC)为物联网的性能、效率、安全性与多功能性设立新标准;

配套USB网关,轻松实现Wi-

随着与三安光电的碳化硅合资工厂落地重庆,2024年6月,意法半导体与重庆市彭水自治县同步启动了可持续发展合作

凯新达科技 自由之旅 征途同行

NVIDIA Jetson Orin™ Nano Super 开发者套件是一款尺寸小巧且性能强大的超级计算机,重新定义了小型边

德州仪器今日推出了全新的集成式汽车芯片,能够帮助各个价位车辆的驾乘人员,实现更安全、更具沉浸感的驾驶体验

广州飞虹半导体科技有限公司成立于广州越秀区,诚信经营20多年。主要研发、生产、经营:场效应管、三极管等半

近日,半导体存储品牌企业江波龙与工业和信息化部电子第五研究所(中国赛宝实验室,以下简称“电子五所”)在江波龙

深圳迈巨微电子有限公司深耕锂电池管理芯片领域,围绕电池健康和安全,电池电量计算二个核心技术能力,提供完善的

点击查看更多

北京科能广告有限公司深圳分公司 版权所有

分享到微信

分享到微博

分享到QQ空间

推荐使用浏览器内置分享

分享至朋友圈