热门标签

月初,TechInsights在Blog上发了这样一篇文章,谈台积电和三星这两家foundry厂在4nm工艺上“造假”的事实...

前年10月,我在知乎回答了一个问题“如果Intel用14nm做出的CPU宣称是10nm的工艺,会有人发现吗?”当时觉得这个问题有趣,就试答了一下。我们认为,这么做大概率不行;从研究机构、用户和foundry/fab厂自身三个角度,都很难把这件事情圆过去。6Tvesmc

不过今年8月初,TechInsights在Blog上发了这样一篇文章,谈台积电和三星这两家foundry厂在4nm工艺上“造假”的事实。主要是基于TechInsight对于4nm工艺的剖析和拆解,认为台积电和三星所谓的4nm,和5nm工艺基本没有区别,却和客户一起对外宣称用上了4nm工艺...6Tvesmc

这件事在我们看来似乎有其合理性,又相当荒诞。不过此事也某种程度表现出,尖端制造工艺再不似往日那般迭代神速,连半代工艺更新(或BKM更新)都如此缓步。前几天“手机晶片达人”在微博发布消息甚至提到“TSMC内部决定放弃N3工艺,因为客户都不用,转2023下半年量产降本的N3E工艺;N3成本高,design的window又很critical;连Apple都放弃N3工艺。”6Tvesmc

且不论信息可靠性如何,联合TechInsights所说“假的”4nm一事,都可知尖端工艺领域,技术推进有多不易。要知道此前我们多番报道过3nm工艺已经延后了半年。如果初代N3节点真的被放弃,那么台积电这边的3nm工艺大规模量产实际的延后时间就将近1年了;Intel直呼内行。6Tvesmc

6Tvesmc

6Tvesmc

TechInsights在博文中提到,首款采用台积电N4工艺的芯片是联发科天玑9000;而TechInsights对这款手机芯片做了分析,发现“关键工艺尺寸和台积电更早的N5产品完全一致”,所以“台积电宣称的4nm产品是假的(sham),也包括联发科宣称其为4nm处理器”。6Tvesmc

三星这边的情况则更窘:三星自家的Exynos 2200芯片采用4nm工艺,高通骁龙8 Gen 1也采用三星4nm工艺。但TechInsights认为,骁龙8 Gen 1用的分明就是5nm工艺。“为了避免用户选择竞品(lusting for one processor over the other),这两家公司决定将骁龙8 Gen 1作为4nm工艺来发布”。6Tvesmc

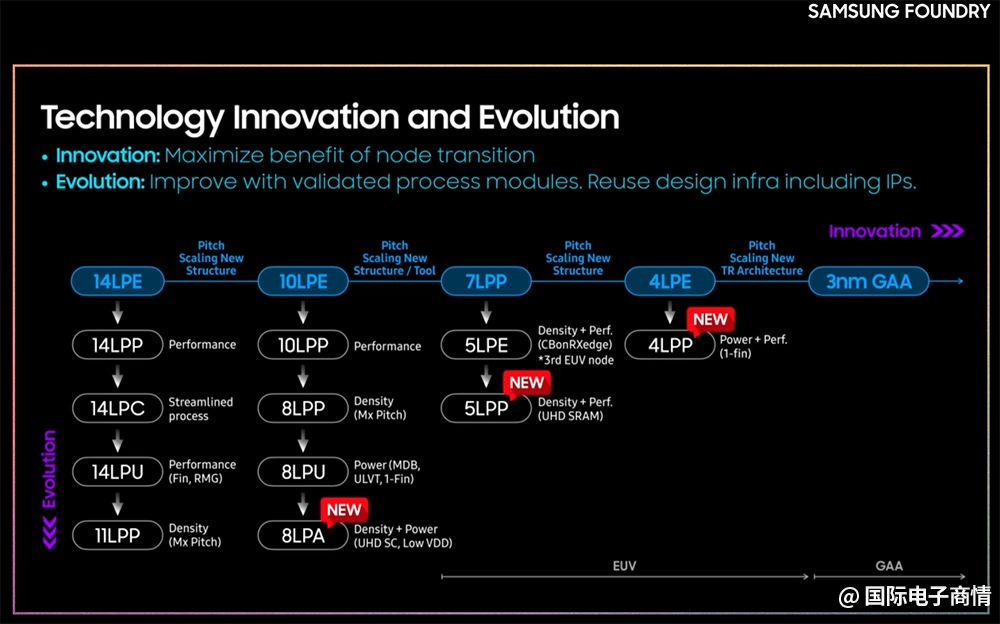

此前似乎有消息说骁龙8 Gen 1采用的乃是一种名为4LPX的工艺——而不是三星公开宣传中的4LPE。TechInsights认为4LPX在物理尺寸上(physically)和5LPE是没有区别的,所以三星也撒了谎。6Tvesmc

但这其中还有个细节,就是三星Exynos 2200还真的应用了4LPE工艺——这算是名副其实的4nm工艺了吧。只是悲惨的是Exynos 2200作为当代唯一“真正的”4nm芯片,在良率、能效等各方面的表现上都颇为糟糕,“尤其是其全新的图形引擎”——这一点我们在此前的分析文章里也谈过。三星4LPE实则比不上台积电N5。6Tvesmc

TechInsights表示,预计真正的台积电4nm将出现于今年9月将陆续上市的高通骁龙8+ Gen 1,以及苹果A16,即N4P工艺。6Tvesmc

至于这两家foundry厂为什么要这么做,TechInsights在博文中说,三星和台积电一直在工艺技术上赛跑;尤其是三星,虽然在工艺技术上略逊于台积电,却一直期望实现赶超。此前三星说要在2021年推4nm工艺——也就是比5nm问世时间大约晚一年。台积电原计划是要在5nm上市的2年以后再上4nm的,但听到三星这么一说,就决定把N4节点的时间“提前(pull in)”2个季度。6Tvesmc

但我们知道,尖端制造工艺可不是市场决定提前2个季度,技术就能立马跟上的,所以才有了这样一幕奇特的局面。6Tvesmc

因为TechInsights针对骁龙8 Gen 1、天玑9000的剖析报告售价都非常高,我们一时半会儿也看不到针对台积电和三星“假”的4nm工艺的分析结果。不过实际上,这个问题就又回到了工艺节点的命名问题上。6Tvesmc

有关尖端工艺节点的命名问题,我们此前也特别撰文谈过。总结一句话就是:当代的尖端制造工艺,“nm”前面的这个数字本质上并不代表任何实际的晶体管或器件物理尺寸。从250nm节点以后,几纳米数字就不再指代常规意义上的栅极长度(gate length),而只有技术迭代的象征意义。6Tvesmc

那么行业里有没有一个规范,来要求不同foundry厂统一节点迭代后的命名称谓呢?还真的就没有。所以理论上,foundry厂想把自家新工艺叫任何名字都可以——当然这其中还存在行业、道德、竞品的各种客观约束,但这就不是技术层面要讨论的重点了。6Tvesmc

所以我们此前曾花大篇幅去细谈过,台积电和三星的5nm虽然都叫5nm,但它们技术层面的差别还是比较大的;而且这两家foundry厂的5nm在其各自技术更新路线图上所处的位置还大相径庭。6Tvesmc

从这个层面来看,foundry厂给自家技术节点起什么名字,那都是人家的自由。连Intel都能给已经量产的工艺节点改名,台积电和三星为什么就不行呢?(虽然Intel节点的改名,也是对台积电和三星感到万般无奈的结果)“我说它是4nm,那就是4nm,你管得着吗”这类表达...6Tvesmc

有关工艺命名,还有另一个常见(但也并不成文的)规则。由于半导体制造工艺技术进步比以前慢了很多,所以foundry厂和芯片设计厂商才会大力宣传同代节点的演进(如N5→N5P/N4),因为工艺完整升级(如N5→N3)中间间隔时间相比从前久了很多。在22nm节点以前,foundry厂几乎是不大宣传这样的小幅工艺改进的。6Tvesmc

N4就属于N5→N3的过渡工艺节点。它远远说不上是N5和N3之间的中间态,明确应为N5的改良工艺,而与N3相去甚远。通过观察同代工艺演进,还不难发现一个事实:一般同代工艺内的器件尺寸(晶体管)间距不会发生变化,而仅在标准单元、部分工艺流程、材料方面会有改进。6Tvesmc

所以一般同代工艺演进很难带来大幅度的晶体管密度提升,以及性能、功耗方面的显著革新。不过我们依然会发现,比如台积电说N4相比于N5能够实现6%的die面积缩减。这种芯片面积小幅缩减,或晶体管密度小幅提升,主要是由单元(cell)结构变化带来的,而不是晶体管层面的尺寸缩减。6Tvesmc

当然,基于当前半导体制造尖端技术难度和成本陡增,这种工艺改良也不简单。改良版工艺有时还能实现降本增效;对于foundry厂而言,还能成为其下一代完整节点更新的技术积累;也是两代完整工艺节点之间的缓冲,不仅是技术的缓冲,更是市场的缓冲。6Tvesmc

基于同代工艺演进这种规则,器件层面没有尺寸缩减实属正常;行业甚至存在Intel这种,为进一步提升性能,同代工艺演进(+++)平均“晶体管密度”变低的状况。6Tvesmc

6Tvesmc

6Tvesmc

不过同代工艺技术演进,也存在晶体管密度大幅攀升的情况。比如说三星5LPE工艺,它在三星路线图上并不属于7LPP的完整迭代,而是7LPP同代工艺演进(这也是三星5nm与台积电5nm定位差异的一个体现)。5LPE在器件尺寸方面相比7LPP几乎没有变化,但仍然实现了“晶体管密度”的大幅攀升;这主要是通过引入新型的UHD单元库达成的。6Tvesmc

而三星4LPE工艺,起码在三星路线图上看来,是7LPP以后的一次完整迭代(虽然其性能、功耗方面的改进幅度相比5LPE相当小)。这令三星4LPE扮演的角色与台积电N4又很不一样。如果抛开“几纳米”主流话语权在台积电手上这件事,4LPE在三星foundry内部的地位应当也是很重要的,因为两家foundry厂的技术演进节奏是不一样的。6Tvesmc

基于5LPE仅为7LPP的同代工艺改良,4LPE才是7LPP的完整迭代;而N5是N7的完整迭代,N4仅为N5的同代工艺改良——理论上市场就不应该期待4LPE和N4同时到来。这也更好理解为什么在原计划的路线图里,台积电N4当晚于三星4LPE到来。不过市场竞争似乎不大理这一套,如文首提及TechInsights的猜测那般。6Tvesmc

4LPE在Exynos 2200之上的如约而至因此就很好解释了。只不过三星在4LPE节点上表现仍然拉垮。《三星面临的大麻烦,又岂止是3nm工艺落后》一文就提到了高通并没有选择4LPE工艺,而是一种名为4LPX的5nm改良款工艺,密度稍逊于4LPE——这则消息同样来自TechInsights。6Tvesmc

TechInsights在对骁龙8 Gen 1的拆解中发现,4LPX工艺中很难找到4nm特性(hardly found '4nm' features)。SemiAnalysis此前撰文称,三星foundry近两代工艺的parametric yield良率糟糕,且从Exynos 2200的表现来推测,高通最终没有选择4LPE是在情理之中的。6Tvesmc

至于特供的“4LPX”究竟是不是原版5LPE,那就只有三星和高通知道了。这里涉及到一个问题,就是既然“4nm”不存在一个基准,那么怎么理解4LPX和N4是不是4nm的问题呢?我们认为,这主要取决于foundry厂做出来的成品是否与其前期宣传中提到的参数提升一致。如果一致,就可以认为该技术是4nm;如果打了折扣则可认为存在“造假”的可能性。6Tvesmc

只是一方面我们也不清楚TechInsights针对工艺研究达到怎样的深度。原本如果只是器件和单元层面的尺寸测量测试,还是很难反映工艺是否有改良或迭代。不过三星自己的路线图都明确了4nm是一次器件尺寸缩减的完整工艺升级,所以4LPX的存在的确有些说不过去。所以4LPX更像是个市场动作。6Tvesmc

至于台积电,N4不做尺寸缩减说不说得过去?那就有更大的商榷余地了。毕竟N4真的就只是N5的改良款。只不过从TechInsights的措辞来看,天玑9000的N4大约也未能达成此前台积电宣传中的die面积缩减。加上台积电“提前”N4工艺亮相时间,大概率是为了赶上三星4LPE发布时间点,其相比于N5改良的多少也的确值得怀疑。6Tvesmc

N4是否是“真正”的4nm这个问题原本是没有标准答案的。但很快N4P的问世,将有助于我们了解N4究竟是台积电4nm的如约而至,还是台积电的一次市场动作。有趣的是,英伟达在今年的GTC Spring上提到自家新款GPU将基于台积电4N工艺——据说是台积电为英伟达定制的4nm工艺,那么对所谓“4N”工艺的分析大概又会很有趣。6Tvesmc

6Tvesmc

6Tvesmc

随着半导体尖端制造工艺技术成本的持续跃升,foundry厂市场竞争的一个重要方向就是持续吞噬对手的市场,否则只能被迫降低投入、减缓技术迭代速度,并在竞争中失去优势。因为成本增速已经快于行业本身的增速。未来尖端制造工艺或许还会面临更大的不确定性,尤其是当器件结构步入GAAFET之后,而4nm节点的这一市场现状不过是个前菜罢了。6Tvesmc

微信扫一扫,一键转发

关注“国际电子商情” 微信公众号

国际电子商情讯,3月17日晚间,深圳英集芯科技股份有限公司发布公告称,公司决定终止购买辉芒微电子(深圳)股份有限公司控制权,公司芯股票自2025年3月18日开市起复牌。

全球前十大IC设计公司全年营收合计达2498亿美元,同比激增49%。其中,英伟达以1243亿美元营收蝉联榜首,占据前十总份额的50%,与其他厂商形成断层式差距。

继宝马、奔驰裁员之后,奥迪也开始宣布裁员。

最近,国产存储领域出现了一个新进者——思远半导体。这家在智能穿戴、TWS耳机、移动电源、BMS等领域深耕十数年的电源管理芯片(PMIC)Fabless,如今把业务范围成功地扩展到了存储电源领域。

3月17日午间,华大九天发布公告称,正在筹划通过发行股份及支付现金等方式,购买芯和半导体的控股权,其股票自当日开市时起开始停牌,预计在不超过10个交易日的时间内披露本次交易方案。

近日,国家互联网信息办公室、工业和信息化部、公安部、国家广播电视总局联合发布《人工智能生成合成内容标识办法》(以下简称《标识办法》),该办法自 2025年9月1日起正式施行。

日前,美国国会众议院以口头表决的方式一致通过了编号H.R.1166的《与依赖外国对手电池脱钩法》,禁止美国国土安全部采购宁德时代、比亚迪、远景能源、亿纬锂能、海辰储能和国轩高科六家中国企业生产的电池。

2025年3月16日,中共中央办公厅、国务院办公厅印发《提振消费专项行动方案》并发出通知。其中涉及到“人工智能+”行动,促进“人工智能+消费”。

国际电子商情讯,据彭博社资深记者马克·古尔曼(Mark Gurman)最新爆料,苹果正秘密打造一款颠覆性产品——iPhone 17 Air,该机型将以“史上最薄iPhone”姿态冲击市场,该机型将无SIM卡槽,机身厚度仅5.5毫米,较现有iPhone薄约2毫米。

"以后只有用我们的鸿蒙PC了。”

国际电子商情讯,继闪迪、美光宣布涨价之后,业内也传出长江存储也将涨价。根据中国闪存市场报道,根据渠道反馈,长江存储零售品牌致态也将于4月起面向渠道上调提货价格,幅度或将超过10%。

“全国人民买得起、想不到的产品”

美通社消息,3月14日,“2025英飞凌消费、计算与通讯创新大会”(ICIC2025)在深圳举行。本届大会汇聚600多位业界精

近日,湖南省工信厅发布了《2025年湖南电子信息制造业重点项目名单》,涵盖先进计算、音视频、新一代半导体、人

3月15日,质鼎集团公众号消息,惠科东莞平板显示集群电子商务项目二期正式开工。

富士康、台积电、广达、华硕、联发科、友达光电等中国台湾20家电子企业2024年第四季度和全年财报汇总。

近年来,LED显示屏市场持续演进。回顾2024年,行业呈现出哪些发展态势?展望2025年及未来,市场又将面临哪些机遇与

近日,索尼正式发布新一代RGBLED背光技术系统,可实现4000尼特峰值亮度。索尼计划该系统将于2025年开始量产,并将

AI芯片是半导体最大的增长点,先进封装则是制造AI芯片的关键技术。此前英伟达H100成本约3000美元,而用先进封装

截止2024年底,17家欧美固态电池企业融资总额已突破42亿美元。

曾几何时,中国半导体几乎不断有大基金投资、大项目上马,以及美国制裁的新闻。长期处于聚光灯下,中国半导体成为

Dynabook在退出十年后宣布重返美国消费市场。

Canalys最新数据显示,受到消费需求激增8%的推动,2024年第四季度中国大陆的PC市场开始复苏,同比增长2%。

根据TrendForce集邦咨询最新调查,2024年第四季由于Apple(苹果)手机生产进入高峰,以及中国部分地方提供消费补贴

德州仪器近日推出了全球超小型 MCU,进一步扩展了品类齐全的 Arm® Cortex®-M0+ MSPM0 MCU 产品组合。

创新是企业持续发展最大的价值。

“闪迪(Sandisk)又回来了!”在3月12日的存储年度盛会CFMS MemoryS 2025上,闪迪公司全球产品副总裁Eric Spa

摩尔斯微电子推出合规的Wi-Fi HaLow片上系统(Soc),开启欧洲连接技术新纪元。超低功耗、远距离连接功能现已为

CFMS | MemoryS 2025已圆满落幕,期间包括三星电子、长江存储、铠侠、美光、闪迪、高通、Arm、慧荣科技、S

Hyperlux™ ID iToF 系列将深度测量距离提升至最远 30 米,提高工业环境中的生产效率和安全性

26TB大容量CMR HDD助力WD Red Pro与G-DRIVE/G-RAID系列专业级产品矩阵,赋能数据存储拓展与生产力跃升

全新一代MCU可以满足各种区域控制架构和电气化系统需求,助力汽车制造商向软件定义汽车(SDV)过渡。

将出色的高

聚洵半导体科技(上海)有限公司(Gainsil Semiconductor Technology)于2016年成立于上海张江科学城,是一家全球

领域新成果领域新成果4月必逛电子展!AI、人形机器人、低空飞行、汽车、新能源、半导体六大热门新赛道,来NEPCO

后量子加密技术帮助保护数字基础设施免受量子计算机在将来带来的潜在威胁。

英飞凌坚信低碳化和数字化是未来十年的关键驱动力,半导体在应对能源挑战和推动数字化转型中扮演着重要角色。

近期热点

EE直播间

更多>>

在线研讨会

更多>>

点击查看更多

Copyright © 2000-2025 eMedia Asia Ltd. All rights reserved.

北京科能广告有限公司深圳分公司 版权所有

分享到微信

分享到微博

分享到QQ空间

推荐使用浏览器内置分享

分享至朋友圈