瑞萨PCIe 6.0/Gen6时钟器件方案应用范围及技术参数详情

2022-04-17 11:09:40

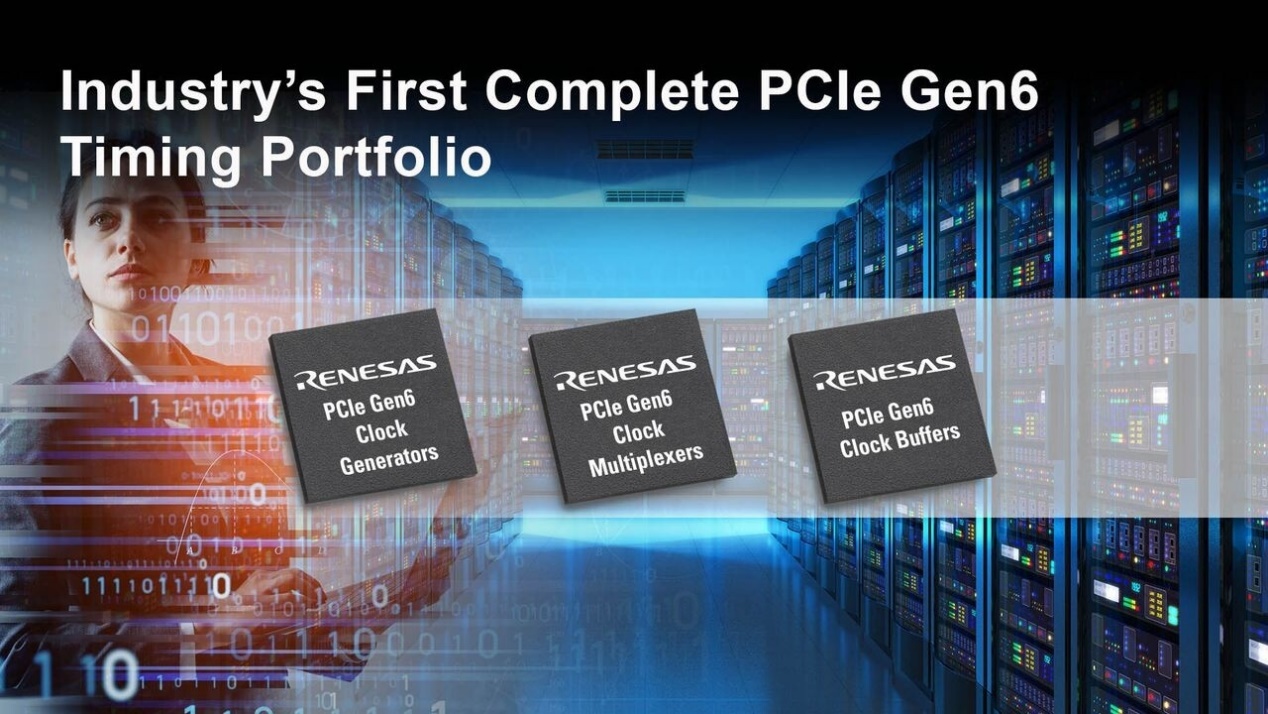

22近日,瑞萨发布了符合最新PCIe 6.0规范的Gen6 Timing时钟器件,请看其应用范围和技术详情。

近日,瑞萨发布了符合最新PCIe 6.0规范的Gen6 Timing时钟器件,请看其应用范围和技术详情。QCiesmc

QCiesmc

QCiesmc

应用范围QCiesmc

日本瑞萨电子发布的全球首个PCIe 6.0标准的计时方案,包括11款时钟缓冲器(clock buffer)、4款多路复用器(multiplexer),以及时钟发生器(clock generator),为数据中心、云计算、网络、高速工业应用提供完整的产品线。QCiesmc

瑞萨电子时钟产品部副总裁Zaher Baidas表示:“PCIe Gen6时钟器件将成为数据中心、高速网络和其它应用中新设备的核心。正如我们针对前几代标准所推出的产品一样,瑞萨率先为客户打造了PCIe Gen6时钟解决方案,以支持这些新的、更高性能的系统。同时,瑞萨的客户也十分了解并信任我们所拥有技术专长和市场洞见,能够确保他们的产品满足未来的需求。”QCiesmc

Semico Research首席分析师Rich Wawrzyniak表示:“通过为PCIe Gen6提供首个分离时序解决方案,瑞萨使客户能够开发下一代高性能系统。看到这种新功能所带来的创新很有趣,尤其是在考虑新兴Chiplet市场的解决方案如何开始发展时,需要提高速度和带宽作为基本常数。”QCiesmc

技术参数详情QCiesmc

1月份,PCI-SIG组织正式发布了PCIe 6.0标准规范,带宽继续翻倍,x16单向可达128GB/s,而且升级了PAM4脉冲调幅信令、FEC前向纠错机制、FLIT流量控制单元编码,是历代变化最大的一次。此前,Rambus曾全球首个发布了完全符合PCIe 6.0的控制器,支持全部新特性。QCiesmc

瑞萨称,PCIe 6.0带宽提升的同时,要求时钟抖动(ClockJitter)不超过100fps RMS,而瑞萨的RC190xx系列时钟缓冲器、RC192xx系列多路复用器时钟抖动仅仅4fps RMS,等于几乎没有任何噪声。QCiesmc

同时,输入输出延迟为1.4ns,输出输出偏差为35ps,电源电压抑制比(PSRR) -80dB@100kHz,都可以保证充分的系统稳定性,并支持断电容忍(PDT)、弹性启动序列(FSS),以确保一场系统状态下的稳定性。QCiesmc

此外,功耗也比前代产品降低了30%。QCiesmc

瑞萨的PCIe 6.0时钟缓冲器可选4、8、13、16、20、24输出,多路复用器可选2、4、8、16输出,封装尺寸都仅仅3×3毫米。QCiesmc

微信扫一扫,一键转发

关注“国际电子商情” 微信公众号

近日,重庆市人民政府办公厅印发《重庆市推动经济持续向上向好若干政策举措》,提出支持科技领军企业、产业链龙

全球半导体观察 | 2025-02-11 13:41:39

DeepSeek模型虽降低AI训练成本,但AI模型的低成本化可望扩大应用场景,进而增加全球数据中心建置量。

TrendForce集邦 | 2025-02-06 11:44:44

2024年第四季度,全球智能手机出货量同比增长2.6%,达到3.253亿,连续五个季度保持复苏态势。

TechInsights | 2025-02-05 16:36:19

2024年全球智能手机市场增长7%,达到12.2亿部,实现了在连续两年下滑后的反弹。

Canalys_China | 2025-02-05 16:37:37

根据TrendForce集邦咨询最新研究,美国2024年12月非农就业人数和制造业采购经理人指数(PMI)皆优于市场预期,美国

TrendForce集邦 | 2025-01-15 19:11:11

随着传统扩展方式的成本和复杂性上升,先进封装已成为满足人工智能(尤其是大型语言模型训练)性能需求的一种方式

TechInsights | 2025-02-07 15:31:28

2024年第四季度,全球平板电脑出货量同比增长5.6%,达到3990万台。使得2024年全年总出货量达到1.476亿台,同比增

Canalys_China | 2025-02-06 17:46:49

英国品牌评估咨询公司“品牌金融”(BrandFinance)发布“2025年全球品牌价值500强”榜单(Global5002025),苹果

全球企业动态 | 2025-01-26 12:53:32

从拉各斯到内罗毕,从开罗到约翰内斯堡,线下零售渠道依然是非洲智能手机市场的中坚力量,在绝大多数地区贡献了超

Canalys_China | 2025-01-23 17:30:18

近日,Tokyo Electron(以下简称“TEL”)宣布,将在日本宫城县建造一座新的生产大楼,由TEL的制造子公司TEL宫城公司

全球半导体观察 | 2025-02-11 17:19:22

国际电子商情24日讯 21日凌晨发生在中国台湾地区嘉义大埔地区发生的里氏6.4级浅层地震,对台湾省南部的半导体

国际电子商情综合报道 | 2025-01-24 18:39:29

国际电子商情1月27日讯,近日多家国内外报道,国内显示屏大厂京东方(BOE)计划进军半导体芯片领域,目前该公司正寻

国际电子商情综合报道 | 2025-01-27 14:24:33

斥资9500亿韩元收购日本FICT,MBK Partners到底图什么?

国际电子商情综合报道 | 2025-02-07 14:28:35

国际电子商情13日讯 据美国半导体行业协会(SIA)日前发布的数据显示,2024年11月全球半导体销售额达到了578亿美

国际电子商情综合报道 | 2025-01-13 15:21:30

国际电子商情13日讯 据媒体报道,在全球NAND闪存市场供过于求的背景下,三星电子决定将其最大的NAND生产基地—

国际电子商情综合报道 | 2025-01-13 19:07:48

国际电子商情24日讯,被看作“晴雨表”的模拟芯片巨头德州仪器(Texas Instruments Inc.)23日公布了令人失望的20

Elaine Lin | 2025-01-24 15:42:56

国际电子商情5日讯 日本电子巨头松下公司正在考虑出售或缩减其陷入困境的电视业务,集中力量发展人工智能数据

国际电子商情综合报道 | 2025-02-05 15:56:55

2024年,集成电路行业在变革与机遇中持续发展。面对全球经济的新常态、技术创新的加速以及市场需求的不断变化

芯耀辉 | 2025-01-16 11:19:02

雅加达,印尼- 2025年1月14日 - 全球技术解决方案供应商艾睿电子(Arrow Electronics)与印尼初创协会合作(STARFIN

| 2025-01-14 16:15:37

最新Wi-Fi HaLow片上系统(SoC)为物联网的性能、效率、安全性与多功能性设立新标准;

配套USB网关,轻松实现Wi-

摩尔斯微电子 | 2025-01-10 09:25:45

NVIDIA Jetson Orin™ Nano Super 开发者套件是一款尺寸小巧且性能强大的超级计算机,重新定义了小型边

iCEasy | 2025-01-09 15:07:46

德州仪器今日推出了全新的集成式汽车芯片,能够帮助各个价位车辆的驾乘人员,实现更安全、更具沉浸感的驾驶体验

德州仪器 | 2025-01-08 13:45:34

近日,半导体存储品牌企业江波龙与工业和信息化部电子第五研究所(中国赛宝实验室,以下简称“电子五所”)在江波龙

江波龙 | 2024-12-31 16:08:49

深圳迈巨微电子有限公司深耕锂电池管理芯片领域,围绕电池健康和安全,电池电量计算二个核心技术能力,提供完善的

| 2024-12-31 15:22:55

点击查看更多

北京科能广告有限公司深圳分公司 版权所有

分享到微信

分享到微博

分享到QQ空间

推荐使用浏览器内置分享

分享至朋友圈